74LS138集成电路:引脚图,电路和应用

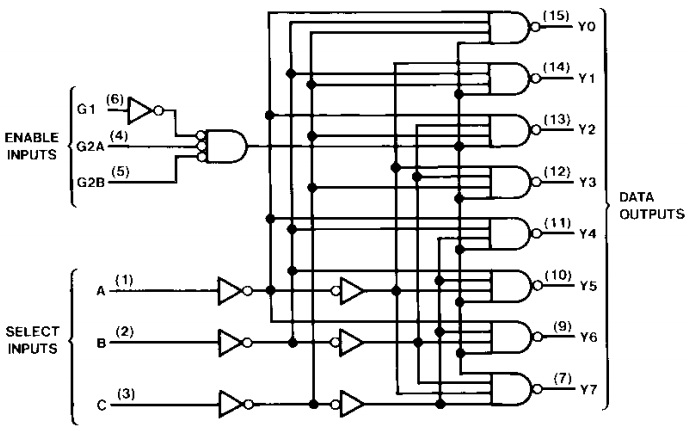

的译码器74 ls138集成电路使用先进的技术,如硅(Si)门TTL技术。这些适用于不同的应用程序,如内存地址解码或数据路由。这些应用通常与TTL电路相结合,具有高抗噪声和低功耗的特点。这个74LS138 IC有3个二进制选择输入,如A, B,和c。如果IC被激活,那么这些输入引脚将决定8个通常高o/ps中的哪一个会变成低。使能引脚为两个有效低引脚和一个有效高引脚。译码器的输出可以驱动10个低功耗的肖特基TTL等负载,并且所有的输入都可以通过二极管对VCC和地面进行静电放电来保护免受伤害。本文讨论了74LS138集成电路的概述:3 ~ 8线解码器IC。

什么是74LS138 IC?

IC 74LS138是一个3到8线解码器集成电路来自74xx家族transistor-transistor-logic-gates。该集成电路的主要功能是对应用程序进行解码、解复用。该IC的设置是可访问的3输入8输出设置。该集成电路主要用于高性能的内存译码以及数据路由等应用。这些ic可用于最小化系统解码影响的高性能存储系统。该IC包括三个使能引脚(其中两个引脚是有效的低电平和一个有效的高电平)减少了外部门的必要性。24行译码器的实现可以在不使用外部逆变器的情况下完成,以及32行译码器需要单个逆变器

这种IC主要用于de-multiplexing应用程序的帮助下,一个使能引脚,如数据输入引脚。这个IC的输入也被夹住了肖特基二极管这是高性能的包含线路振铃和系统设计简化。

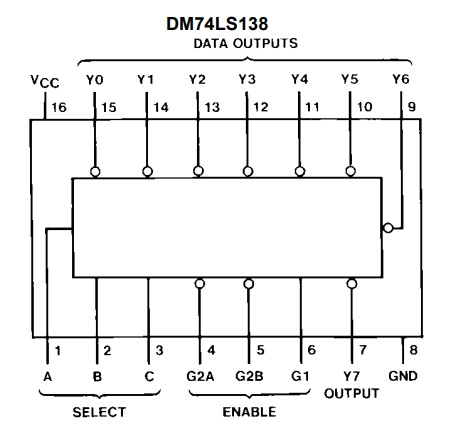

74 ls138销配置

的IC 74LS138是一种16脚集成电路,该IC的每个引脚将在下面讨论。类似的74LS138 IC有

- 引脚1 (A):地址输入引脚

- Pin2 (B):地址输入引脚

- Pin3 (C):地址输入引脚

- Pin4 (G2A): Active low enable引脚

- Pin5 (G2B): Active low enable引脚

- Pin6 (G1): Active high enable pin

- Pin7 (Y7):输出引脚

- Pin8 (GND):接地引脚

- Pin9 (Y6):输出引脚6

- Pin10 (Y5):输出引脚5

- Pin11 (Y4):输出引脚4

- Pin12 (Y3):输出引脚3

- Pin13 (Y2):输出引脚2

- Pin14 (Y1):输出引脚1

- Pin15 (Y0):输出引脚0

- Pin16 (VCC):电源引脚

74 ls138集成电路功能

的74LS138集成电路的特性包括以下。

- 这种集成电路是专为高速而设计的

- 解码能力

- 集成3使能引脚,简化级联

- 防静电安全

- 公正的传播延迟

- 电源电压范围为1.0V-5.5V

- 输入电压允许优于VCC

- 标准传播延迟为21nS

- 功耗低32mw

- 肖特基夹紧高性能

- 工作温度范围为-40℃~ +125℃

74LS138 IC如何使用?

为了了解集成电路的工作原理,让我们设计一个简单的电路基本的电子元件如下所示。在上面的电路中,输出连接到发光二极管说明哪个o/p引脚是低的,IC的输出是倒置的。

这里我们使用了单个器件,因此G2A和G2B引脚的连接连接到GND,然后连接g1到vcc以激活芯片。

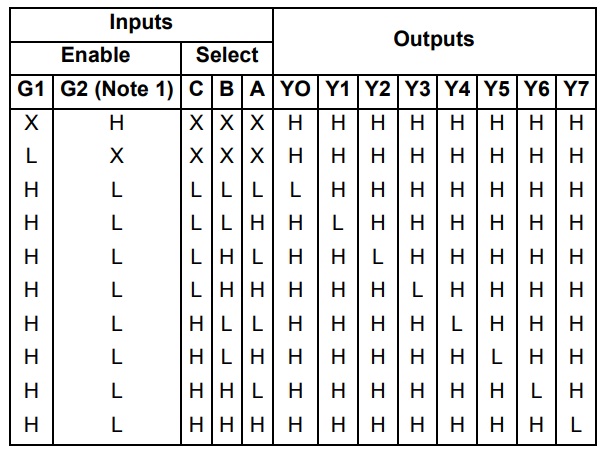

这里三个按钮代表这个设备的三个i/p行。为了更好地理解这个概念,让我们理解下面的真值表。在上面的表格中,H-HIGH, L-LOW和X-不关心。使能引脚G1、G2A和G2B,其中G2=G2A + G2B。

在上面的表格中,第一行即G1, G2是需要正确连接的使能引脚,否则不管所有的i/p线,以及o/p线,都会很高。一旦连接了enable引脚,就可以连接输入线以获得输出。

连接后,如果所有开关都不推,Y0将是低的,剩余的o/p将是高的,如上表格所示。当B1被推入时,A0为HIGH, Y1为LOW,其余为HIGH。仅按B2时,A1为高,Y2为低,其余为高。通过这种方式,我们可以通过切换三个开关(B1, B2和B3)来理解整个真值表,输入是A0, A1和A2。

74LS138 IC的应用

的IC 74LS138的应用包括以下。

- 行解码器

- 记忆回路

- 服务器

- 数字系统

- 行De-multiplexing

- 电信电路

因此,这就是一切3至8线解码器74LS138 IC数据表。如前所述,这种IC特别设计用于高性能内存解码,否则在数据应用路由中需要很少的传播延迟时间。存储单元的数据交换速率决定了任何应用程序的行为&任何类型的暂停都是不可接受的。因此,IC74LS138线解码器是这种应用的理想选择。因为,该IC的保持时间比通常的内存访问时间要少,这意味着译码器引入的有效系统保持时间对性能的影响是微不足道的。

图片来源:德州仪器公司