数字电子中的锁存基础知识bob足球体育app

在数字电子技术bob足球体育app,门闩是一种逻辑电路,它也被称为a双稳态多谐振荡器.因为它有两种稳定状态即高活性和低活性。它的工作原理类似于存储设备,通过反馈通道保存数据。只要设备被激活,它就会存储1位数据。一旦启用,立即锁存可以更改存储的数据。一旦启用信号被激活,它就会不断地尝试输入。根据使能信号的高电平或低电平,这些电路可以在两种状态下工作。当锁存电路处于有源高电平时,两者的i/ps都是低电平。类似地,当锁存电路处于有源低状态时,两个i/ps都是高的。

不同类型的门闩

锁存可分为不同类型,包括SR锁存,因此锁大门,D锁、门控D门闩、JK门闩和T门闩。

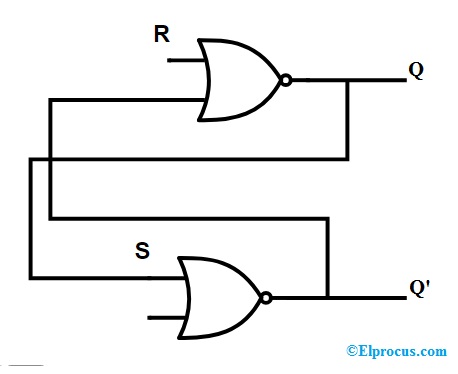

SR闭锁

一个SR(设置/重置)锁是一个异步设备,它独立工作的控制信号依赖于s状态和r输入。下面展示了使用2-NOR门和交叉环路连接的SR-latch。这些门闩可以用NAND盖茨也;然而,这两个输入被交换和取消。所以它被称为SR ' -latch。

只要给锁存器的s线一个高输入,输出Q就会变高。在反馈过程中,当s输入再次降低时,输出Q将保持高电平。通过这种方式,门闩就像一个存储设备一样工作。

同样地,给锁存器的r线一个高输入,然后Q输出变低(和Q '高),然后锁存器的内存将有效地重置。当锁存器的两个输入都很低时,它就会保持在较早的设置状态或复位状态。的状态转换表或真值表SR锁存器如下图所示。

| 年代 | R | 问 | 问的 |

| 0 | 0 | 门闩 | 门闩 |

0 |

1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

1 |

1 | 0 | 0 |

当两个输入同时高时,就会出现问题:它被告知并发生成高Q和低Q。这会在电路中产生一个竞争条件,要么触发器实现了一些改变,首先将响应另一个并声明自己。最好,逻辑门是相等的,设备将处于一个不确定阶段的未定义条件。

封闭的SR闭锁

在某些情况下,当门闩能或不能闩上时,可能很受欢迎。an的简单扩展SR闭锁只不过是封闭的SR闭锁.它给出了一个Enable行,在信息可以锁存之前应该驱动高电平。虽然控制线是必要的,但锁存器是不同步的,因为即使在使能脉冲的中间,输入也会改变输出。

当一个使能的输入是低的,从门的o/ps也必须更少,因此Q & Q输出保持对早期信息的锁存。简单地说,当使能i/p高时,就可以改变闩锁的位置,如表格所示。正如使能线所述,门控SR闩锁在通向SR闩锁的过程中是相等的。有时,使能线是CLK信号;然而,它是一个读/写频闪。

CLK |

年代 | R | 问(t + 1) |

0 |

X | X | 问(t)(没有变化) |

| 1 | 0 | 0 | 问(t)(没有变化) |

1 |

0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

1 |

1 | 1 | X |

D锁

数据锁存器是门控sr -锁存器的简单扩展,消除了输入状态不可接受的可能性。因为门控SR锁存器让我们在不使用S或R输入的情况下固定输出,我们可以通过用相反的驱动器驱动两个输入来消除其中一个i/ps。我们消除一个输入&自动使它与剩余输入相反。

当使能线高时,D锁存器输出D的输入,否则,当使能输入最后一个高时,输出就是D的输入。这就是它被称为透明门闩的原因。当启用时,锁存器被称为透明锁存器,信号直接通过它传播,因为如果它不存在。

E |

D | 问 | 问的 |

0 |

0 | 门闩 | 门闩 |

0 |

1 | 门闩 | 门闩 |

1 |

0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

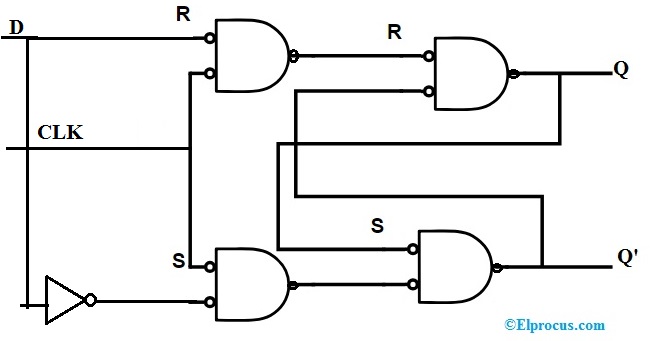

封闭的D锁

一个封闭的D锁门控锁存器的设计简单,通过改变一个门控SR-latch,而门控SR-latch的唯一变化是输入R必须被修改为倒s。门控锁存器不能由使用NOR的SR-latch形成,如下所示。

每当CLK其他启用是高的,o/p锁存任何东西是在D的输入上。类似地,当CLK是低的,那么最终启用高的D i/p是输出。

CLK |

D | 问(t + 1) |

| 0 | X | 问(t) |

1 |

0 | 0 |

| 1 | 1 | 1 |

锁存器的电路根本不会经历Race状态,因为只有D输入被反向提供给两个输入。因此,不可能有类似的输入状态。因此,d锁存器电路可以安全地应用于多种电路中。

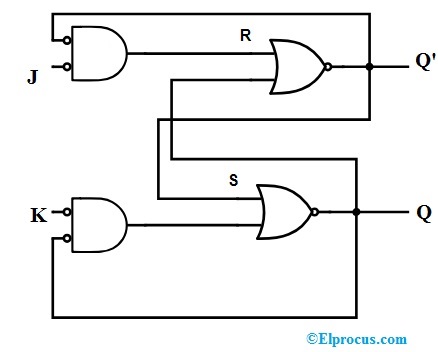

JK门闩

两JK门闩,以及RS锁扣,是类似的。此锁存器包括两个输入,即J和K,如下逻辑门图所示。在这种类型的门闩中,不清晰的状态已经被移除了。当JK锁存输入高时,输出将被切换。我们在这里能观察到的唯一不同是输出对输入的反馈,这在rs锁存器中是不存在的。

T门闩

的T门闩可以在JK锁存输入短路时形成。当锁存器的输入高时,T锁存器的功能是这样的,然后输出被切换。

门闩的优点

的门闩的优点包括以下。

- 与之相比,锁存器的设计非常灵活FFs(人字拖)

- 门闩使用更少的电力。

- 锁存器在高速电路设计中的性能是快速的,因为这些在设计中是异步的,不需要CLK信号。

- 门闩的形状很小,占地面积小

- 如果闩锁电路的操作没有在设定的时间内完成,它们就会从其他电路借用必要的时间来完成操作

- 与之相比,锁存器给出侵略性时钟触发器电路.

缺点的门闩

的缺点的门闩包括以下。

- 有可能会影响竞态条件,所以这是不太期望的。

- 当锁存器是水平敏感时,就有可能出现亚稳态。

- 由于电路具有电平敏感的特性,分析起来比较困难。

- 该电路可以通过使用一个额外的CAD程序进行测试

应用锁存

的门闩的应用包括以下。

- 一般来说,闩锁是用来保持二进制数编码的位的条件

- 锁存是一种单比特存储元件,广泛应用于计算和数据存储中。

- 门闩用于电路,如功率门控和时钟作为存储设备。

- D锁存器适用于异步系统,如输入或输出端口。

- 数据锁存在同步两相系统中用于减少传输计数。

因此,这是关于门闩的概述。这些是积木时序电路.这个设计可以用逻辑门来完成。它的操作主要依赖于使能函数的输入。有个问题要问你,门闩的两种工作状态是什么?