什么是BCD计数器:电路及其工作

数字和数字逻辑电路,一个称为a的顺序电路柜台是计算输入脉冲所必需的。计数器由具有应用时钟信号的一组触发器设计。BCD计数器是最广泛使用的数字的类型之一柜台,其中最多10使用施加的时钟信号。它是一个4位二进制数字计数器,计数从1(0001)到10(1010)。在实践中,BCD计数器在0000(0)到1001(9)上以十进制形式计数在时钟信号的应用上。这些类型的计数电路可以74LS90异步十年计数器等集成电路的形式提供。本文概述了BCD柜台或十年柜台。

什么是BCD柜台或十年柜台?

BCD计数器是4位二进制计数器之一,其从0计数到具有应用时钟信号的预定计数。当计数达到预定计数值时,它会重置所有人字拖并开始重新计算。通过使用4 JK触发器设计,从0到9的计数设计,从0到9的计数,并且结果以数字形式表示。达到9(1001)的计数后,它重置并重新开始。

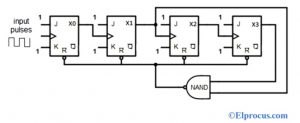

BCD或十年计数器电路

BCD或DEDADE计数器电路是通过使用JK触发器和NAND门设计的。BCD计数器设计非常简单,它需要4 JK触发器,因为它是一个4位二进制计数器。十年计数器的设计如下所示。

从该图中,我们观察到j和k的输出连接到逻辑1.每个触发器的输入脉冲或时钟输入作为输出到下一个触发器,但不是最后一个触发器。CLR输入并行于NAND门输出,以在计数到达时重置所有触发器。

十年柜台运作

在初始阶段(在操作之前),十四计数器的计数是0000.当时钟信号被给出为输入时,操作开始并计数二进制输出。对于第一个时钟脉冲,十年计数器最多可计入9(1001),并且对于下一个时钟输入脉冲,它高达10(1010)。

对于给定时钟信号,十个计数器计数为0到9。当它到达计数时,它会重置所有触发器,重复循环。

当NAND门的输入X1和X3高时,输出将低。如果NAND门的输出连接到透明输入,则它将重置十年计数器的所有拖力的阶段。这意味着当输入脉冲达到0到9时,它停止计数并再次启动计数。

十年柜台的真相表

十年计数器的真相表如下所示。

输入脉冲/时钟脉冲 |

QD. | QC. | QB. | QA. |

0. |

0. | 0. | 0. | 0(重置) |

1 |

0. | 0. | 0. | 1 |

| 2 | 0. | 0. | 1 | 0. |

3. |

0. | 0. | 1 | 1 |

| 4. | 0. | 1 | 0. | 0. |

5. |

0. | 1 | 0. | 1 |

| 6. | 0. | 1 | 1 | 0. |

7. |

0. | 1 | 1 | 1 |

| 8. | 1 | 0. | 0. | 0. |

| 9. | 1 | 0. | 0. | 1 |

它计算十进制输入脉冲,并以二进制形式显示输出。当输入脉冲计数达到9(1001)时,NAND门的输出为零。

NAND门的输入X1和X3解码计数以以二进制形式显示输出。当计数达到9时,它通过从1到0触发NAND门的输出来重置所有触发器。

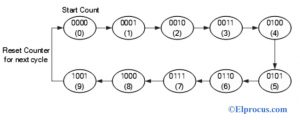

十进制计数器的状态图

十年计数器的状态图如下所示。

BCD计数器或十年计数器具有4 JK触发器,具有16个组合状态,如上图所示。在16个州,使用10。当计数器串联连接时,我们可以根据应用程序数最多1000或1000。

术语模量是计数器具有计数脉冲能力的总数。当计数器计数n-counts时,它达到零,称为模数n-counter。示例是MOD-8计数器,MOD-16计数器等。N位模量二进制计数器的计数范围为0至2N-1。

类似地,BCD计数器是MOD-10计数器,其在从0(0000)到9(1001)计数之后重置为零,表示成交的结果。(这意味着除以10计数)。因此,它被称为二进制编码的十进制计数器(BCD计数器)。它是一个8421代码(二进制重量为4位或位),由4个二进制数字组成,非常容易执行二进制和十进制转换。

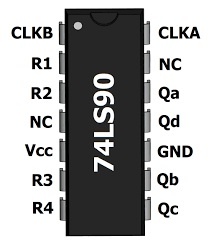

74LS90十年计数器IC描述

74LS90 DEPADE COUNTER IC描述和引脚配置如下所示。它是最广泛使用的14针集成芯片。

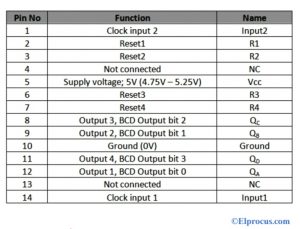

PIN解释

解释

十年计数器是一个简单的4位二进制计数器,具有4个输出 - QA,QB,QC,QD。计数达到计数10,然后每次重置具有二进制输出0(0000)的所有触发器,并再次启动计数周期。复位引脚R1,R2,R3和R4用于设置和复位IC 7490。

当复位引脚R1,R2高并且R3,R4接地时,输出QA,QB,QC,QD设置为0(0000)并重置计数器。

当R3,R4高时,输出设置为9(1001)。通过串联连接更多的IC,可以提高74LS90十四码计数器的计数能力。它存储并表示以上述真理表中所示的小数形式的结果。

BCD计数器或十进制计数器的应用

带有时钟信号的电子电路称为十进制计数器。它是一个4位二进制输入输出电路。BCD计数器或十进制计数器的应用如下

频率计数十年柜台

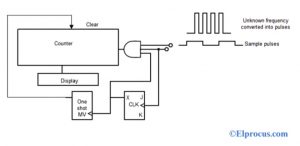

十年计数器是频率计数器设计中使用的二元计数器。使用JK触发器的十年计数器的设计如下所示。

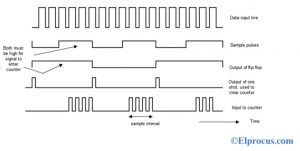

频率计数电路中的十年计数器的目的是找到或计算未知信号的频率。要计数的频率被馈送到一个输入的一个输入,并且样本脉冲被赋予与上图所示的AND栅极的另一输入。

在高样本脉冲处,允许电路将输入转移到计数器。在低样本脉冲处,输入信号被传送到计数器。输入信号的未知频率是反击给出的计数与采样时间间隔的比率。JK触发器保持计数器的输出,其中馈送的第三输入。

当输入信号来自JK触发器而样品脉冲高,然后由计数器显示输出。单次多谐振荡器发送脉冲以在JK触发器的每个高输入信号(正边缘)之后重置计数器。

因此,这一切都是关于BCD计数器的概述-定义,电路,设计,电路操作,真值表,状态图,74LS90十进制计数器,及应用。这里有一个问题要问你:“BCD计数器的优点是什么?””