什么是二进制加法器和减法器

在数字电路,二进制加法器和减法器用于添加和减去二进制数。该电路的操作主要取决于二进制值。这里,电路中的控制信号保持二进制值。它是其中之一组件算术逻辑单元。该电路需要有关半加法器,全加法器,二进制添加和减法的先决条件信息。一次,也可以设计用于执行添加的电路以及减法。本文讨论了二进制加法器和二元减法器的概述。

二进制加法器和减法器

二进制加法器和减法器的概述主要讨论二进制添加电路,二进制加法器(半加法器和全加法器),并联二进制加法器,二进制减法电路,二元减法器(半音减法器(半音减法器)和并联二进制减法器。

二进制添加电路

在数字电路中,可以使用二进制添加的算术运算逻辑门。为此,使用双输入逻辑门,并且与或门略有不同。A或Gate添加两个整数并在两个输入为1时生成一个输出。但是当我们将其与独占或门进行比较时,A或Gate不会获得由于单独的操作而产生的二进制添加。在包容性或门口中,它包括三个O / PS,添加到生成总和。现在,我们可以相互比较这两个盖茨。

这两个逻辑门之间的主要区别主要包括或栅极执行整数,而EX-OR门执行二进制操作。

什么是二进制加法器?

二进制加法器是一种数字电路,主要用于执行两个二进制数的算术运算,如添加。二进制加法器可以通过串联连接来设计与完整的加法器电路。第一个完整加法器的输出携带连接到第二个完整加法器的输入。这些电路分为半加法器,全加法器和并联加法器。

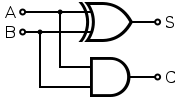

半加法器

半加法器是一种电子电路用于执行两个二进制数字的添加。半加法器添加两个二进制数字,并生成一个像输出一样的两个输出并带有值。半加法器的输入是A&B,而输出是总和和携带。通用表示使用像And Gate和XOR逻辑门等逻辑门。

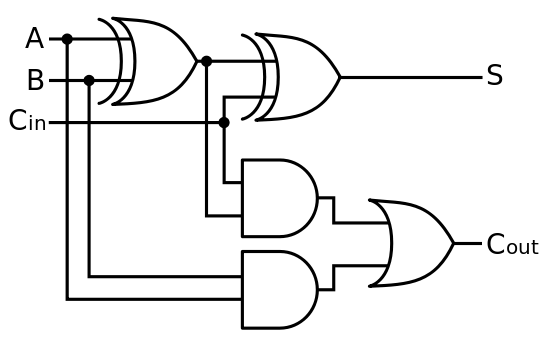

完整的加法器

完整的加法器是一种用于执行三个二进制数的电子电路。完整加法器添加了三位二进制数字,并生成两个像输出一样的输出并携带值。半加法器的输入是A,B和CIN,而输出是SUM和COUT。完整的加法器是两个半加栅的组合,其中像和XOR门一样通过或门连接。请参阅此链接以了解更多信息半加法器和完整的加法器。

并行二进制加法器

并行二进制加法器是组合电路,设计有各种完整的加加法器,它们并联连接。在一个并行二进制加法器中,否。完整的加法商主要取决于否。在那里的比特。

可以使用逻辑门进行并行二进制加法器的设计。逻辑电路内的关联模块看起来像两个加法器的逻辑电路,如半加法器和全加法器。

二元减法电路

减法是算术功能,其中从另一个数字中减去一个数字以获得相同的数量。要减去另一个数字的数字被称为minuend。类似地,从Minuend中减去的数字称为子系统。与二进制添加相同,这也包括4可行的替代操作,其中可以从Minuud位中减去每个子系统下拉位。

但是在第二条规则中,与子系统中的比特相比,Minuend的比例较低,因此1贷款才能完成减法。与加法器电路相关,这些电路也分为半减法器,全减法器和并行减法器。

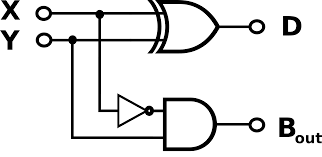

一半减法者

相同的组合逻辑电路,如半音电路用于减去两个单位数字。它包括两个输入以及两个输出。输入是A,B,而输出是借用和差异。请参阅此链接以了解更多信息一半减法者。

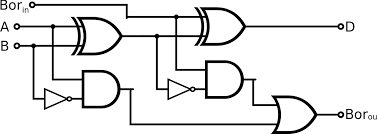

完整的减法者

相同的组合逻辑电路,如半音电路用于减去两个单位数字。它包括三个输入以及两个输出。输入是A,B和BIN,而输出是借用和差异。请参阅此链接以了解有关完整的减法器的更多信息。因此,该减法器包括通过考虑较低的显着阶段的借用来执行三位减法的能力。请参阅此链接以了解更多信息完整的减法者。

并行二元减法器

并行二进制减法器是一种数字电路,用于找到两个二进制数的差异,其在长度上通过在并联的等效对等对的比特上操作。该减法器的设计可以用多种方式完成,如减法器和所有完整的减法器的组合,使用子系统的补充。

因此,这是关于二元的加法器和减法器包括二进制添加电路,二进制加法器,如半加法器和全加法器,并联二进制加法器,二元减法电路,二元减法器,如半部减法器和全减法器,也是平行二进制减法器。这是一个问题,什么是平行加法器/减法者?