使用3到8解码器的电路设计为4到16个解码器

解码器是一个组合电路由逻辑门构成。它是编码器的反面。译码电路用于将一组数字输入信号转换为其输出的等价十进制码。对于n个输入,解码器给出2^n个输出。在本文中,我们将讨论使用3到8个解码器的4到16个解码器电路设计。

编码器是组合电路,其将一组信号变为代码。对于'2 ^ n'输入,编码器电路给出了'n'输出。

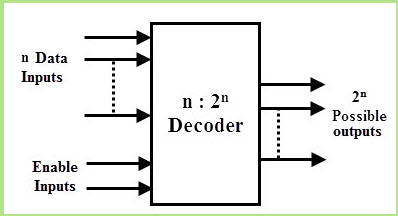

下图显示了解码器的框图。

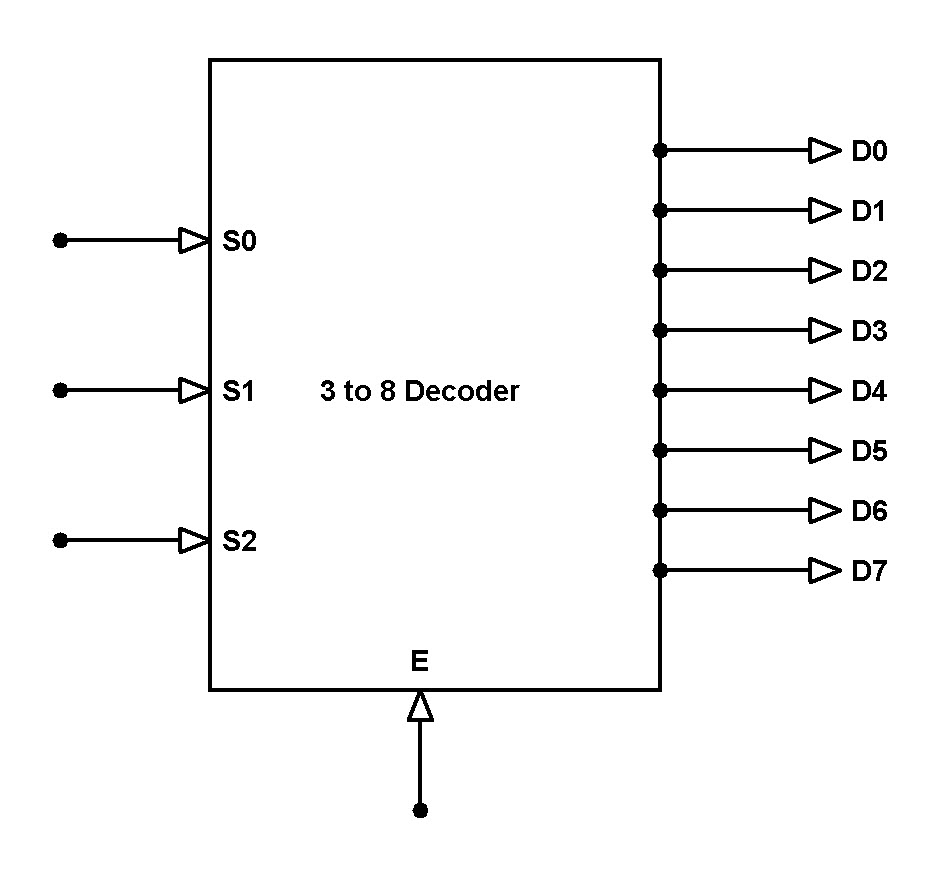

3到8解码器

这个解码器电路为3个输入提供8个逻辑输出。电路是用AND和NAND组合.它需要3个二进制输入并激活8个输出中的一个。

线路图

解码器电路只有在使能引脚高时才能工作。

真值表

当使能(E)引脚为低电平时,所有输出引脚都很低。

| S0 | S1 | S2 | E | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 |

| x | x | x | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

使用3到8解码器的电路设计为4到16个解码器

一个译码器电路较高的组合电路是通过添加两个或多个较低的组合电路来获得的。4 ~ 16解码器电路由2个3 ~ 8解码器电路或3个2 ~ 4解码器电路得到。

当两个3到8解码器电路合并时,使能引脚作为两个解码器的输入。当使能引脚在一个3到8解码器电路高时,那么它在另一个3到8解码器电路低。

真值表

使能(E)引脚充当3到8个解码器电路的输入引脚之一。

| E | 一个 | B | C | Y0 | 日元 | Y2 | Y3 | Y4 | 日元 | 日元 | 日元 | 日元 | 今年上半年 | 日元 | 去年 | 日元 | Y13 | Y14 | Y15 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

4到16解码器的电路图

解码器的应用

- 在每一个无线通信bob的是什么网站在美国,数据安全是主要关注的问题。译码器主要通过设计标准的加解密算法来保证数据通信的安全性。bob的是什么网站

- 解码器用于音频系统将模拟音频转换为数字数据。

- 用作解压缩器,将压缩数据(如图像和视频)转换为解压缩形式。

- 解码器使用电子电路将计算机指令转换成CPU控制信号。

因此,这都是关于4到16的解码器电路设计使用3到8的解码器电路。此外,任何关于本文或bob体育棋牌你可以在下面的评论区给我们留言。有个问题要问你,启用引脚编码器/解码器的用途是什么?

为什么用E ?

嗨,达塔

这里的“E”只是使能引脚。这使引脚为负,并使电路非活动

精彩的帖子。谢谢分享。?