使用FPGA生成具有可变占空比的PWM信号

本文解释了产生脉冲宽度调制使用VHDL对FPGA具有可变占空比的信号。PWM具有固定频率和可变电压。本文还讨论了数字时钟管理器,用于通过减小时钟信号的偏差来降低时钟频率。固定频率用于产生使用比较器产生PWM信号的输入数据。电子公司使用其标准和协议设计专用于其产品的硬件,这使得最终用户根据其需求重新配置硬件的挑战。这一要求硬件导致了新的客户可配置段的增长现场可编程集成电路称为fpga。

脉冲宽度调制(PWM)

脉宽调制在通信、通信等领域有着广泛的应用bob的是什么网站控制系统。在控制系统中可以使用不同的方法产生脉宽调制。本文采用硬件描述语言(VHDL)生成PWM,并在FPGA上实现。在FPGA上实现PWM可以更快地处理数据,控制器架构可以针对空间或速度进行优化。

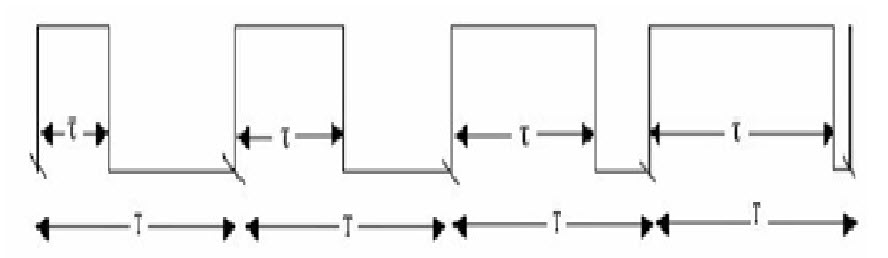

PWM是一种技术为受控时间提供逻辑'0'和逻辑'1'。它是一种信号源,涉及调制其占空比,以控制发送到负载的功率量。在PWM中,方波的时间段保持恒定,并且信号保持高的时间变化。

PWM以其输出的输出产生脉冲,使得高度和低点的平均值与PWM输入成比例。信号的占空比可以变化。PWM信号是具有不同占空比的恒定周期方波。也就是说,PWM信号的频率是恒定的,但是信号的时间段保持高并且如图所示的变化。

硬件描述语言(VHDL)

VHDL是一种语言,用来描述行为的数字电路设计。VHDL被工业界和学术界用于数字电路的仿真。它的设计可以被模拟和翻译成适合在硬件上实现的形式。

PWM架构

为了生产输入数据,使用高速N位自由运行计数器生成PWM,其输出与寄存器输出进行比较,并在比较器的帮助下存储所需的输入占空比。比较者当这两个值相等时,Output设置为1。此比较器输出用于设置RS锁存器。计数器的溢出信号用于重置RS锁存器。的RS锁存器输出给出所需的PWM输出。这个溢出信号也用于在寄存器中加载新的n位占空比。PWM具有固定频率和可变电压。这个电压值从0V变化到5v。

基本的PWM产生信号,给出PWM的输出,需要一个比较器来比较两个值。第一个值表示由N位计数器产生的方信号,第二个值表示包含有关占空比信息的方信号。每当出现溢出时,计数器就产生负载信号。一旦负载信号激活,寄存器加载新的占空比值。负载信号也用于复位锁存器。锁存器输出是PWM信号。这随占空比值的变化而变化。

FPGA是什么?

FPGA为现场可编程门阵列。它是一种广泛应用于电子电路中的器件。fpga是半导体器件其中包含可编程逻辑块和互连电路。它可以在制造后根据需要的功能进行编程或重新编程。

FPGA的基本知识

当电路板被制造时,如果它包含FPGA作为它的一部分。在制造过程中对其进行编程,之后可以重新编程以创建更新或做出必要的更改。FPGA的这一特性使其有别于ASIC。专用集成电路(ASIC)是为特定的设计任务定制的。在过去FPGA被用于开发低速、复杂性和体积设计,但今天FPGA将很容易将性能障碍推到500MHz。

在微控制器中,芯片是为客户设计的,他们必须编写软件并将其编译为十六进制文件加载到微控制器。这个软件可以很容易地替换,因为它存储在闪存中。在fpga中,没有处理器来运行软件,我们是设计电路的人。我们可以配置一个简单的与门或复杂的多核处理器FPGA。为了创建一个设计,我们编写硬件描述语言(HDL),它有两种类型- Verilog和VHDL。然后用BITGEN将HDL合成为位文件,对FPGA进行配置。FPGA将配置存储在RAM中,即没有电源连接时配置丢失。因此,每次供电时都必须配置它们。

FPGA的建筑学

FPGA是预制的硅芯片,可以电动编程以实现数字设计。称为SRAM的第一静态存储器的FPGA用于使用配置位流配置逻辑和互连。今天的现代EPGA包含大约3,30,000个逻辑块和大约1,100个输入和输出。

FPGA的结构由三个主要组件组成

- 可编程逻辑块,实现逻辑功能

- 可编程路由(互连),实现函数

- I / O块,用于进行片外连接

PWM信号的应用

PWM信号广泛应用于控制领域。如控制直流电机,控制阀,泵,液压等。下面是PWM信号的几个应用。

- 加热系统,慢速时间为10至100Hz或更高。

- 直流电机5至10KHz

- 电源或音频放大器20至200 kHz。

这篇文章都是关于发电PWM信号使用FPGA的可变占空比。此外,对于关于本文的电子项目或疑虑的任何帮助,您可以通过评论下面给出的评论部分与我们联系。

您好,正如我所知,所有控制器都能够通过它自己生成PWM,但是有6个PWM技术用于生成PWM信号。因此,我怀疑是FPGA使用的PWM技术,如正弦技术,空间矢量,三角洲或多个等等。它使用哪种技术。