什么是半减法器:使用逻辑门的电路

在电子产品领域中,每个组件都适用的bob足球体育app最重要的概念是“逻辑门“。由于逻辑门的概念在各种功能中实现,例如集成电路,传感器,切换目的,微控制器和处理器,加密和解密目的,以及其他功能。除此之外,还有广泛的逻辑门应用。有许多类型的逻辑门,如加法器,减法器,满加法器,全减值器,半减法器和许多其他人。因此,本文提供了集体信息半减法器电路那半减法器真相表和相关的概念。

什么是半减法者?

在进行讨论半个减法器之前,我们必须知道二进制减法。在二进制减法中,减法过程类似于算术减法。在算术减法中,在二进制减法中使用基部2号系统,而二进制数用于减法。所得到的术语可以用差异和借用表示。

半音是最重要的组合逻辑电路用于数字电子产品bob足球体育app。基本上,这是一种电子设备或其他术语,我们可以将其作为逻辑电路。该电路用于执行两个二进制数字减法。在上一篇文章中,我们已经讨论过半加法器的概念和一个完整的加法器电路它使用二进制数进行计算。类似地,减法器电路使用二进制数(0,1)来减法。半减法器的电路可以用两个构建逻辑门即NAND和EX-or Gates。该电路给出了两个元素,如差异以及借用。

与二进制减法一样,主要数字为1,我们可以在子系统第1次优于Minuend 0而且由于这一点,因此,借款将需要。以下示例给出了两个二进制位的二进制减法。

第一个数字 |

第二个数字 | 区别 | 借 |

0. |

0. | 0. | 0. |

1 |

0. | 1 | 0. |

| 0. | 1 | 1 | 1 |

| 1 | 1 | 0. | 0. |

在上述减法中,两位数可以用A和B表示。可以减去这两位数并将所得位作为差异和借用。

当我们观察前两个和第四行时,这些行之间的区别,那么差异和借用类似,因为subtrahend比minuend小。同样,当我们观察第三行时,从子系统中减去minuend值。因此,差异和借用位为1,因为Subtrahend数字优于Minuend Digit。

这种组合电路是任何类型的重要工具数字电路了解输入和输出的可能组合。例如,如果减法器有两个输入,则所产生的输出将是四个。下表中提到了一半减法器的O / P,它将表示差异位以及借用位。电路的真相说明可以通过使用如前或逻辑门和栅极操作之后的逻辑门来完成,然后是非门。

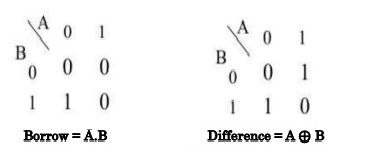

使用真相表k-map.如下所示。

这半减法器表达使用真理表和k映射可以衍生成

区别(d)=(X'y.+XY.')

=x⊕y

借用(b)= x'y

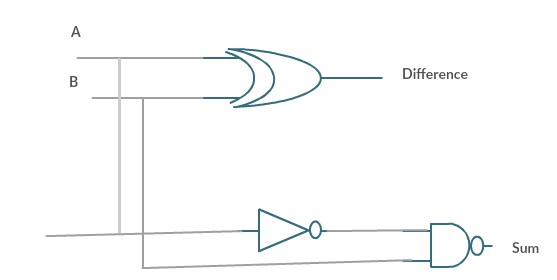

逻辑电路

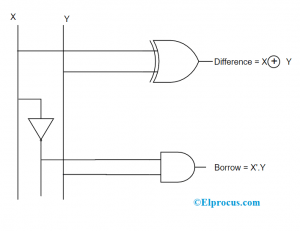

这半减法器逻辑电路可以使用逻辑门来解释:

- 1 xor门

- 1不是门

- 1和门

代表是

半减法器块图

半减法器的框图如上所示。它需要两个输入以及给出两个输出。这里输入用A&B表示,输出是差异和借用。

上述电路可以设计有前或&Nand栅极。这里,NAND门可以通过使用和而不是栅极来构建。因此,我们需要三个逻辑门来制造半个减法器电路即,即出口或门,而不是门和NAND门。

和而不是栅极的组合产生一个名为NAND门的不同组合门。EX-OR GATE输出将是差分位,NAND门输出将是相同输入A&B的借用位。

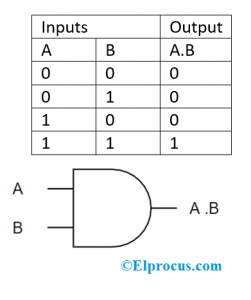

和门

AND-GATE是一种类型的数字逻辑门,具有多输入和单个输出,并且基于输入的输入组合它将执行逻辑结合。当此门的所有输入都很高时,输出将很高,否则输出将低。具有真实表的逻辑图和门的逻辑图如下所示。

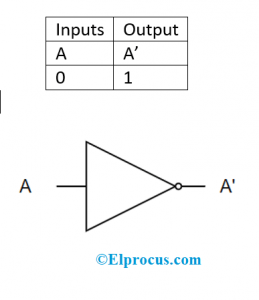

不是门

NOT-GATE是一种类型的数字逻辑门,具有单个输入,并且基于输入输出将被反转。例如,当NOT门的输入很高时,输出将低。具有真相表的NOT-GATE的逻辑图如下所示。通过使用这种类型的逻辑门,我们可以执行NAND和NOR门。

前或门

独家或或门或门是一种类型的数字逻辑门,具有2输入和单个输出。此逻辑门的工作取决于或门。如果此门的任何输入高,则EX-OR门的输出将很高。前或如下所示的符号和真理表。

使用NAND门的半减法器电路

减法器的设计可以通过使用逻辑门像NAND门和前或门。为了设计这个半减法器电路,我们必须知道这两个概念即差异和借用。

如果我们谨慎监视,它非常清楚的是,由该电路执行的各种操作,该操作与前栅操作准确地相关。因此,我们可以简单地使用前或门来实现差异。以同样的方式,通过使用像逻辑门的混合物和门和不门的混合可以简单地实现由半加法器电路产生的借用。

该HS也可以通过使用或栅极来设计,在那里它需要5个也需要施工。电路图半音除载器使用或门显示为:

真理表

第一位 |

第二位 | 区别 (前或出局) |

借 (NAND) |

0. |

0. | 0. | 0. |

| 1 | 0. | 1 | 0. |

0. |

1 | 1 | 1 |

| 1 | 1 | 0. | 0. |

VHDL和TestBench码

半减法器的VHDL代码如下所述:

图书馆IEEE;

使用IEEE.STD_LOGIC_1164.ALL;

使用ieee.std_logic_arith.all;

使用ieee.std_logic_unsigned.all;

实体半_sub1是

端口(A:在STD_Logic;

B:在std_logic;

hs_diff:out std_logic;

HS_BORD:OUT STD_LOGIC);

结束half_sub1;

Half_sub1的架构行为是

开始

hs_diff <= xor b;

hs_borrow <=(不是a)和b;

这HS的测试铃声代码如下所述:

图书馆IEEE;

使用IEEE.STD_LOGIC_1164.ALL;

实体hs_tb是

结束hs_tb;

HS_TB的建筑HS_TB是

组件HS.

端口(A:在STD_Logic;

B:在std_logic;

hs_diff:out std_logic;

HS_BORD:OUT STD_Logic

);

结束组件;

信号A:std_logic:='0';

信号B:std_logic:='0';

信号hs_diff:std_logic;

信号HS_BORD:std_logic;

开始

UUT:HS端口地图(

a => a,

B => B,

HS_DIFF => HS_DIFF,

hs_borrow => hs_borrow

);

stim_proc:process.

开始

<='0';

b <='0';

等待30 ns;

<='0';

b <='1';

等待30 ns;

a <='1';

b <='0';

等待30 ns;

a <='1';

b <='1';

等待;

结束过程;

结尾;

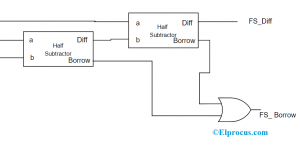

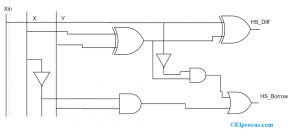

使用半部减法器的全减法器

完整的减法器是一种组合设备,通过使用两个位和minuend和subtrahend来操作减法功能。电路考虑借用先前的输出,它有三个具有两个输出的输入。三个输入是Minuend,subtrahend和从之前的输出收到的输入,借用,两个输出是差异和借用。

真相表完整的减法者是

| 输入 | 输出 | |||

| X | y | 阴 | FS_DIFF. | FS_BORROR. |

| 0. | 0. | 0. | 0. | 0. |

| 0. | 0. | 1 | 1 | 1 |

| 0. | 1 | 0. | 1 | 1 |

| 0. | 1 | 1 | 0. | 1 |

| 1 | 0. | 0. | 1 | 0. |

| 1 | 0. | 1 | 0. | 0. |

| 1 | 1 | 0. | 0. | 0. |

| 1 | 1 | 1 | 1 | 1 |

使用上述真相表,用于使用半减法器实现全减值器的逻辑图AD电路图如下所示:

半减法器的优点和局限性

半减法器的优点是:

- 该电路的实施和构造简单易

- 该电路在数字信号处理中消耗最小功率

- 可以以提高的速度执行计算功能

该组合电路的局限性是:

尽管在许多运营和功能中有一半减法器的广泛应用,但有很少的限制和这些是:

- 来自以前的输出,半音计电路不会接受“借入”,其中这是该电路的重要缺点

- 随着许多实时应用程序在减量大量的比特上运行,半音流因子设备不保持减去许多位的任何能力

半减法器的应用

半减法器的应用包括以下内容。

- 半部减法器用于减少音频或无线电信号的力

- 有可能用于放大器减少声音失真

- 一半减法器是用于alu处理器

- 它可用于增加和减少运营商,并计算地址

- 半音计用于减去最低有效列数。对于多位数字的减法,它可以用于LSB。

因此,从上面的半离子反射器理论,最后,我们可以通过使用该电路来关闭,我们可以从另一个电路从另一个二进制比中减去,以提供差异和借用的输出。同样,我们可以使用NAND Gates电路以及盖茨设计半音点。要知道的其他概念是什么是什么半音计Verilog代码以及如何绘制RTL示意图?