主从触发器电路及其工作

这组合电路不要使用任何内存。因此,输入的前方位置不包括对电路的当前情况的任何结果。尽管,顺序电路包括存储器,因此输出取决于输入意味着输出可以基于输入改变。这些电路的工作可以通过利用先前的电路输入,CLK,存储器和输出来完成。本文讨论了主从触发器的概述。但是在知道这个触发器之前,人们必须了解关于基础知识人字拖像SR翻转和JK触发器一样。

什么是主奴隶触发器?

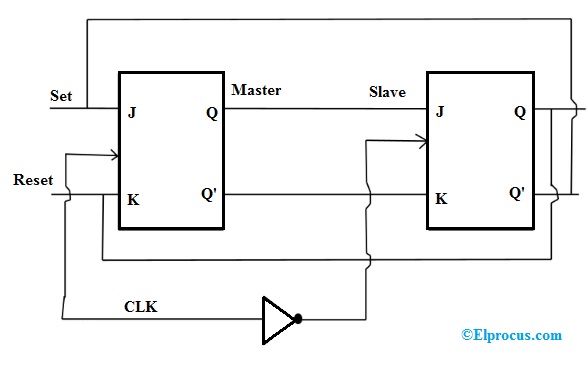

基本上,通过串联连接,可以使用两个JK FF设计这种触发器。其中一个ffs,一个ff作为主服务器以及其他ff作为奴隶工作。这些FF的连接可以如此如此如此,主FF输出可以连接到从属FF的输入。这里可以连接来自Slave FF的输出连接到主FF的输入。

在这种类型的FF中,一个逆变器也使用添加到两个ffs。可以以这样的方式完成逆变器连接,使得反转的CLK脉冲可以连接到从属FF。在其他术语中,如果CLK脉冲为主FF为0,则CLK脉冲将为从FF为1。类似地,当CLK脉冲为主FF为1时,对于从属FF,CLK脉冲将为0。

主奴隶FF工作

每当CLK脉冲高到高电平,即可以分离奴隶;J&K等输入可能会改变系统的状况。

从FF可以被分离,直到CLK脉冲变低(即为0)。当CLK脉冲返回到低态时,可以将数据从主FF传输到从FF,最终得到o/p。

首先,主FF将在正级别触发,而从属FF将以负电平触发。由于这个原因,主FF首先响应。

如果J=0 & K=1,那么主FF ' Q '的输出到从FF的输入K,并且CLK强制从FF RST(复位),因此从FF复制主FF。

如果j = 1&k = 0,则主FF'Q'将进入从属FF的输入j和CLK的负转换设置从属FF,并复制主设备。

如果J=1 & K=1,那么它切换到CLK的正跃迁,因此从节点切换到CLK的负跃迁。

如果J和K都为0,那么FF可以固定,Q保持不变。

时间图

- 当主机的CLK脉冲和o / p都很高时,它仍然很高,直到的时钟由于状态存储了很低。

- 目前,当CLK脉冲再次变为高度并仍然很低,直到CLK再次变为高电平,掌握再次变为低电平。

- 因此,切换进行CLK周期。

- 每当CLK脉冲为1时,MASTER都被设置为ORE,因此,从机器O / P保持'0',直到CLK留1。

- 当CLK为低电平时,从奴隶变为操作,然后保持“1”,直到CLK再次变成'0'。

- 切换在整个过程中进行,而O / P在一个周期内更改一次。

- 这使得该触发器作为同步装置,因为它仅通过了具有CLK信号时序的数据。

因此,这是关于主奴隶的触发器。从上面的信息来看,我们可以得出结论,这个FF可以用两个FF而内置,即主站和从属。当一个FF像主电路一样动作时,它在CLK脉冲的前沿激活。类似地,当另一个FF像从电路一样动作时,它在CLK脉冲的下降沿激活。