上拉电阻和实际示例之间的差异

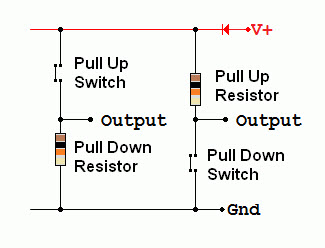

任何微控制器嵌入式系统利用I / O信号与外部设备通信。最简单的I / O形式通常被说明为GPIO(通用输入/输出)。当GPIO电压电平低时,它处于高或高阻抗状态时,上拉和下拉电阻用于确保GPIO始终处于有效状态。通常,GPIO设置在A上微控制器作为I / O.作为输入,微控制器PIN可以采用其中一个状态:高,低,浮动或高阻抗。当I / P上方被驱动I / P是高阈值时,它是一个逻辑。当I / P在I / P下方被驱动,这是低阈值的,输入是逻辑0。在浮动时或高阻抗状态,I / P级别不断高或低。为了确保I / P的值始终处于已知状态,使用上拉和下拉电阻器。上拉和下拉电阻的主要功能是拉压电阻将信号拉到高状态除非它被驱动得低;并且,下拉电阻将信号拉到低状态,除非它被驱动得高。

什么是电阻?

电阻是许多人中最常用的组件电子电路和电子设备。电阻的主要功能是,它限制了电流流到其他组件。电阻器采用欧姆法的原则,这些原则是由于抗性而耗散。电阻单位是欧姆,欧姆的符号显示在电路中的电阻。有众多电阻类型在市场上提供不同的尺寸和评级。它们是金属膜电阻器,薄膜电阻器和厚膜电阻,卷绕电阻器,网络电阻,表面电阻,安装电阻器,可变电阻器和特殊电阻器。

考虑两个电阻串联连接,然后通过箭头指示相同电流I流过两个电阻器和电流的方向。当两个电阻在并联连接时,当两个电阻处于两台电阻器时,电势下降v是相同的。

上拉电阻

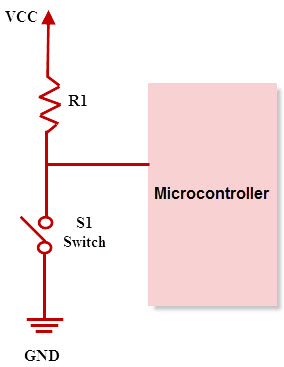

上拉电阻是简单的固定值电阻器,其连接在电压供应和特定引脚之间。这些电阻用于数字逻辑电路为了确保引脚处的逻辑电平,从而导致输入/输出电压是不存在的驱动信号的状态。数字逻辑电路由三种状态包括高,低,浮动或高阻抗等。当引脚未被拉到较低或高逻辑电平时,则发生高阻抗状态。如图所示,这些电阻用于通过将值拉到高状态来解决微控制器的问题。开关打开时,微控制器输入将浮动,仅在开关关闭时才会下降。典型的上拉电阻值为4.7kilo欧姆,但可以根据应用程序进行更改。

使用拉压电阻的NAND门电路

在该项目中,上拉电阻直到逻辑芯片电路。这些电路是测试拉压电阻的最佳电路。基于低信号或高信号的逻辑芯片电路工作。在该项目中,NAND门被视为逻辑芯片的示例。NAND门的主要功能是当NAND门输入的任何一个低时,然后输出信号很高。以相同的方式,当NAND门的输入很高时,输出信号很低。

使用下拉电阻器的所需组件和栅极电路是NAND栅极芯片(4011),10kilo OHM电阻-2,按钮-2,330Ohm电阻器和LED。

- 每个NAND门由两个I / P和一个O / P引脚组成。

- 两个按钮用作到AND门的输入。

- 上拉电阻值是10千克欧姆,其余组件是330欧姆电阻和LED。330欧姆电阻串联连接以限制电流到LED

下面示出了使用I / PE中的I / PE中的2下电阻的NAND门的电路图。

在该电路中,向芯片提供电力,它被送入5V。因此,+ 5V被给予销14,并且PIN7连接到地。上拉电阻连接到NAND栅极输入。拉压电阻连接到NAND栅极和正电压的第一输入。按钮连接到GND。当不按下按钮时,NAND门输入高。按下按钮时,NAND栅极输入低。对于NAND门,I / PS都必须低,以获得高输出。为了工作猫头鹰电路,您必须按下两个按钮上。这显示了上拉电阻的良好有用性。

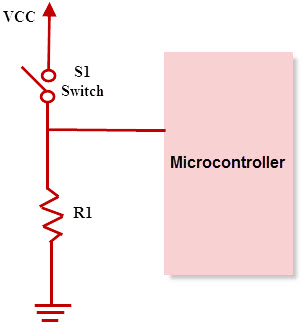

下拉电阻

作为上拉电阻,下拉电阻也以同样的方式工作。但是,它们将销拉到低值。下拉电阻连接在微控制器和接地端子上的特定销之间。拉下电阻的示例是下图所示的数字电路。开关连接在VCC和微控制器引脚之间。当开关在电路中关闭时,微控制器的输入是逻辑1,但是当开关在电路中打开时,下拉电阻将输入电压拉下来(逻辑0或逻辑低值)。拉下电阻应具有比逻辑电路的阻抗更高的电阻。

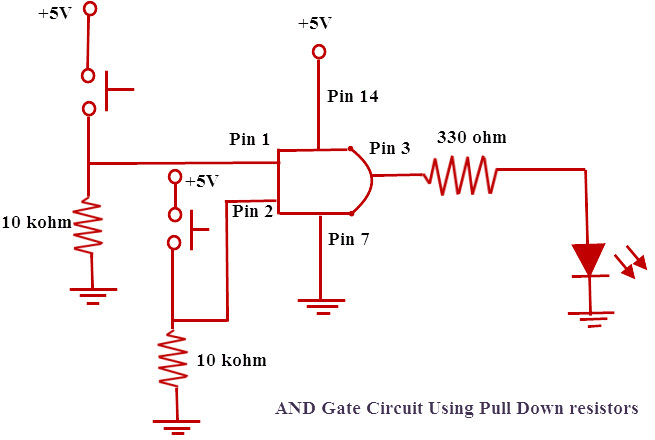

和栅极电路使用拉下电阻

在该项目中,下拉电阻连接到逻辑芯片电路。这些电路是测试下拉电阻的最佳电路。逻辑芯片电路基于低信号或高信号工作。在该项目中,并作为逻辑芯片的示例进行门。当和门的两个输入都很高时,AND门的主要功能是高电平的。以相同的方式当和门的输入低电平时,则输出信号很低。

使用下拉电阻器的所需组件和栅极电路是栅极芯片(SN7408),10kilo OHM电阻-2,按钮-2,330欧姆电阻和LED。

- 每个和门由两个I / P和一个O / P组成

- 两个按钮用作到AND门的输入。

- 下拉电阻值为10千克欧姆,其余组件是330欧姆电阻器和LED。330欧姆电阻串联连接以限制LED的电流。

下面示出了在I / PE上的I / PE中的2拉下电阻器的和栅极的电路图。

在该电路中,向芯片提供电力,它被送入5V。因此,+ 5V给出销14,并且Pin7连接到地。下拉电阻连接到AND栅极输入。一个拉下电阻连接到AND门的第一输入。按钮连接到正电压,然后,下拉电阻连接到GND。如果不按下按钮,并且门输入将很低。如果按下按钮,并且门输入将很高。对于和门,I / PS都必须高,以获得高输出。为了工作猫头鹰电路,必须按下两个按钮。这显示了下拉电阻的良好有用性。

上拉和下拉电阻的应用

- 上拉和下拉电阻经常使用界面设备喜欢接合切换到微控制器。

- 大多数微控制器具有内置的可编程拉向上/拉下电阻。所以可以直接连接带有微控制器的开关。

- 通常,虽然一些微控制器家族具有上拉和下拉电阻,但是上拉电阻通常比拉下电阻器。

- 这些电阻通常用于A / D转换器提供控制电流流入电阻传感器

- 上拉和下拉电阻用于I2C协议总线,其中,上拉电阻用于允许单个引脚充当I / P或O / P。

- 当它未连接到I2C协议总线时,引脚以高阻抗状态浮动。下拉电阻也用于输出,以提供已知的O / P

因此,这一切都是关于工作的工作和差异与实际例子的上拉和下拉电阻之间的差异。我们相信您对此概念有更好的想法。对于本文或关于本文的任何疑问,您可以获得更好的想法。或者bob体育棋牌,您可以通过评论下面的“评论”部分来联系我们。

感谢您的上拉和下拉电阻的简单解释。对于2个输入的NAND门,两个输入不必低至得到输出高。任何一个输入对于输出都可以很低。

嗨Krishnaprasad.

是的,你是对的。

完全何时我们更喜欢拉出电阻并拉下电阻以及为什么仅拉动电阻大部分使用?

请尽快提供答案

嗨,辛巴亚

使用微控制器(MCU)或任何数字逻辑设备时,上拉电阻非常常见。本教程将解释何时何地使用上拉电阻,然后我们将执行简单的计算以显示提升的原因很重要。

假设您有一个带有一个引脚的MCU配置为输入。如果没有任何连接到引脚并且程序读取引脚的状态,它将高(拉到VCC)或低(拉到地)?很难说。这种现象称为浮动。为了防止这种未知状态,上拉或下拉电阻器将确保引脚处于高状态或低状态,同时也使用低电流。

为简单起见,我们将专注于上升,因为它们比下拉更常见。它们使用相同的概念操作,除了上拉电阻连接到高电压(通常为3.3V或5V,通常被归因于VCC),并且下拉电阻连接到地。

上拉常用于按钮和开关。

使用上拉电阻,输入引脚将在未按下按钮时读取高状态。换句话说,少量电流在VCC和输入引脚之间流动(不是接地),因此输入引脚读取接近VCC。按下按钮后,它将输入引脚直接连接到地。电流流过电阻以接地,因此输入引脚读取低状态。请记住,如果电阻不存在,则按钮将VCC连接到地面,这是非常糟糕的,也称为短暂的。

我希望你对我的解释很清楚。