纹波进位加法器:工作、类型及其应用

在数字电子技术bob足球体育app2位二进制数的相加可以通过使用半加法器。如果输入序列具有三位序列,则可以使用完整的加法器完成添加过程。但是如果输入序列中的比特数量更多,则可以通过使用半加法器完成该过程。因为完全加法器无法完成添加操作。因此,可以使用“纹波携带加法器”来克服这些缺点。这是一种独特的类型逻辑电路用于在数字操作中添加n位数。本文介绍了什么是涟漪 - 携带加法器及其操作的概述。

什么是纹波进位加法器?

多个完整添加剂的结构以级联以提供添加N位二进制序列的结果。该加法器包括其结构的级联完整加法器,因此将在纹波携带加法器电路中的每个完整加法器阶段生成携带。这些全部加法级的这些输出被转发到其下一个完整加法器,并将其应用于其输入。这个过程延续了它的最后一个完整的加法器阶段。因此,每个携带输出位都波纹到完整加法器的下一个阶段。因此,它被命名为“涟漪携带加法器”。它的最重要特征是添加输入位序列,无论序列是4位还是5位或任何。

“在该携带加法器中最重要的点之一是最终输出仅在携带输出由每个完整加法器阶段产生并转发到下一阶段之后已知。因此,使用此携带加法器将导致结果延迟。

纹波进位加法器有多种类型。它们是:

- 4位纹波携带加法器

- 8位脉动进位加法器

- 16位波纹携带加法器

首先,我们将从4位纹波 - 携带加法器开始,然后是8位和16位波纹携带加法器。

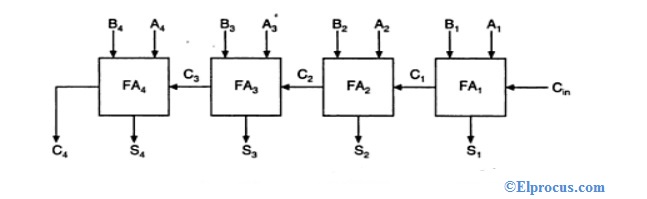

4位纹波进位加法器

下图是4位纹波进位加法器。在这个加法器中,四个全加法器级联。Co是进位输入位,它总是0。当输入进位' Co '应用于两个输入序列A1 A2 A3 A4和B1 B2 B3 B4时,输出为S1 S2 S3 S4和输出进位C4。

4位纹波进位加法器的工作

- 让我们以两个输入序列0101和1010为例。它们代表A4 A3 A2 A1和B4 B3 B2 B1。

- 根据这个加法器的概念,输入进位是0。

- 当Ao和Bo应用于第1个全加法器时,输入进位为0。

- 这里A1 = 1;b1 = 0;CIN = 0.

- 总和(S1)和携带(C1)将根据该加法器的总和进行生成和携带方程。根据其理论,SUM =A1⊕B1cin的输出方程和携带=A1b1⊕b1cin⊕cina1

- 根据该等式,对于第1个完整加法器S1 = 1并携带输出即,C1 = 0。

- 类似于下一个输入位A2和B2,输出S2 = 1和C2 = 0。这里的重点是第二级全加法器得到输入进位,即C1,这是初始级全加法器的输出进位。

- 类似于这将得到最终输出序列(S4 S3 S2 S1)=(11 1 1)和输出携带C4 = 0

- 这是4位输入序列的添加过程,当它应用于此携带加法器时。

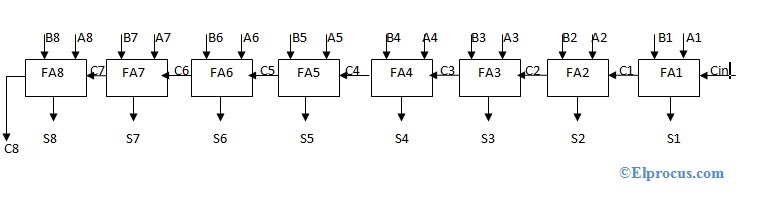

8位波纹携带加法器

- 它由8个级联的全加法器组成。

- 每个完整加法器携带输出连接为输入载物到下一阶段的完整加法器。

- 输入序列由(A1 A2 A3 A4 A5 A6 A6 A6 A6 A)和(B1 B2 B3 B4 B5 B6 B7 B8)表示(S1 S2 S3 S4 S5 S6 S7 S8)。

- 8位纹波 - 携带加法器中的加法过程是在4位纹波 - 随身加法器中使用的相同原理,即,来自两个输入序列的每个比特将与输入携带一起添加。

- 这将在添加两个8位二进制数字序列时使用。

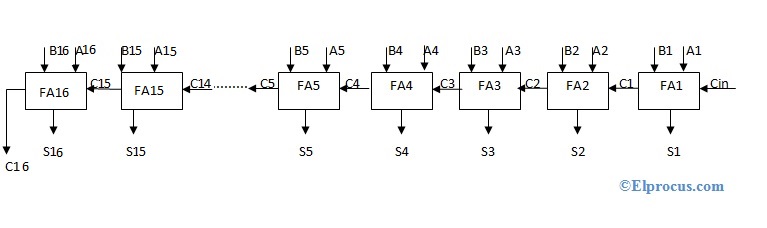

16位波纹携带加法器

- 它由16个以级联形式连接的完整加法器组成。

- 每个完整加法器携带输出连接为输入载物到下一阶段的完整加法器。

- 输入序列用(A1 ..... .)表示A16)和(B1 ...... B16),其相应的输出序列记为(S1 ........S16)。

- 16位纹进位加法器的加法过程与4位纹进位加法器的原理相同,即两个输入序列中的每一位都将与输入进位一起相加。

- 这将使用当两个16位二进制数字相加时的序列。

波纹携带加法器真相表

实际表格下面显示了Ripple-Carry-Adder的所有输入的可能组合的输出值。

| A1 | A2 | A3 | A4 | B4. | B3. | B2 | B1 | S4 | S3 | S2 | S1 | 携带 |

0. |

0. | 0. | 0. | 0. | 0. | 0. | 0. | 0. | 0. | 0. | 0. | 0. |

| 0. | 1 | 0. | 0. | 0. | 1 | 0. | 0. | 1 | 0. | 0. | 0. | 0. |

1 |

0. | 0. | 0. | 1 | 0. | 0. | 0. | 0. | 0. | 0. | 0. | 1 |

| 1 | 0. | 1 | 0. | 1 | 0. | 1 | 0. | 0. | 1 | 0. | 0. | 1 |

| 1 | 1 | 0. | 0. | 1 | 1 | 0. | 0. | 1 | 0. | 0. | 0. | 1 |

| 1 | 1 | 1 | 0. | 1 | 1 | 1 | 0. | 1 | 1 | 0. | 0. | 1 |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0. | 1 |

纹波进位加法器VHDL代码

VHDL (VHSIC HDL)是一种硬件描述语言。这是一种数字设计语言。这个进位加法器的VHDL代码如下所示。

图书馆IEEE;

使用IEEE.STD_LOGIC_1164.ALL;

实体RippleCarryadder是

端口(a:在std_logic_vector中(3到0);

B: in STD_LOGIC_VECTOR (3 down to 0);

Cin:在STD_LOGIC;

输出STD_LOGIC_VECTOR (3 down to 0);

Cout: out STD_LOGIC);

Ripplecarryadder结束;

RippleCarryaddder的架构行为是 - 完整加法器VHDL代码组件声明

组件full_adder_vhdl_code

端口(A:在STD_Logic;

B:在std_logic;

Cin:在STD_LOGIC;

S: out STD_LOGIC;

Cout: out STD_LOGIC);

结束组件;

- 中级携带宣言

信号C1,C2,C3:STD_Logic;

开始

- 端口映射完整加法器4次

FA1: full_adder_vhdl_code port map(A(0), B(0), Cin, S(0), c1);

FA2: full_adder_vhdl_code port map(A(1), B(1), c1, S(1), c2);

FA3:fuS_adder_vhdl_code端口映射(a(2),b(2),c2,s(2),c3);

FA4: full_adder_vhdl_code port map(A(3), B(3), c3, S(3), Cout);

端行为;

纹波进位加法器Verilog代码

Verilog代码是一种硬件描述语言。用于数字电路的RTL级设计和验证。这个进位加法器的verilog代码如下所示。

模块ripple_carry_adder(a,b,cin,sum,cout);

输入(03:0);

输入[03:0] b;

输入cin;

输出[03:0]总和;

输出cout;

线(2:0)c;

fulladd a1 ([0], [0], cin, [0], c [0]);

fulladd a2 (b [1], [1] c[0]和[1],c [1]);

Fulladd A3(A [2],B [2],C [1],SUM [2],C [2]);

Fulladd A4(A [3],B [3],C [2],SUM [3],COUT);

endmodule

模块Fulladd(A,B,Cin,Sum,Cout);

输入A,B,CIN;

输出总和,cout;

指定SUM =(a ^ b ^ cin);

分配cout =((a&b)|(b&cin)|(a&cin));

Ripple进位加法器应用

纹波进位加法器的应用包括以下内容。

- 这些进位加法器主要用于n位输入序列之外。

- 这些携带添加剂适用于数字信号处理和微处理器。

波纹携带加法器优势

纹波携带加法器优点包括以下内容。

- 这款携带加法器具有它的优势,如我们可以对N位序列进行添加过程以获得准确的结果。

- 这个加法器的设计不是一个复杂的过程。

波纹携带加法器是当输入位序列较大时,当半加法器和全加法器不执行加法操作时的一种替代方法。但在这里,它会给出输入位序列的输出有一定的延迟。对于数字电路来说,如果电路输出带有延迟将是不可取的。这可以通过进位前瞻加法器电路来克服。