使用PLA设计顺序电路

它的主要缺点是组合电路是,它不使用任何内存来保存当前和以前的状态。因此,以前的输入状态对电路的当前状态没有任何影响。虽然,顺序电路具有存储器,因此输出可以根据输入而变化。这种类型的电路使用先前的输入,输出,时钟和存储元件。这里存储元件可以是锁存或触发器。顺序电路由使用ROM和翻转,PLAS,复杂可编程逻辑器件那FPGA(现场可编程门阵列).在这篇文章中,我们将只讨论如何使用pla设计一个时序电路。

顺序电路的框图如下所示:

使用PLA设计顺序电路

顺序电路可以使用可编程逻辑阵列和触发器来实现。在这种设计中,状态分配可能是重要的,因为使用良好的状态分配可以减少所需的产品项的数量,从而减少PLA所需的尺寸。一个乘积术语,定义为字面值的合取,其中每个字面值要么是一个变量,要么是它的否定。

对于让我们考虑设计一个代码转换器。下表所示状态表可以使用1个PLA和3个PLA实现人字拖如下图所示。此电路配置与基于ROM的基于ROM基于ROM的设计非常相似,不同之处在于ROM由合适尺寸的PLA代替。状态分配导致下面给出的真相表。此表可以存储在PLA中,其中包含四个输入,13个产品术语和四个输出,但与16字ROM相比,这会提高大小的大小。

| x Q1 Q2 Q3 | Z D1 D2 D3 |

| 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 |

1 0 0 1 1 0 1 1 0 1 0 0 0 1 0 1 1 1 0 1 0 0 0 0 1 0 0 0 X X X X 0 0 1 0 0 1 0 0 1 1 0 0 1 1 0 1 0 1 1 0 1 0 0 0 X X X X X X X X |

表:真相表

展示 状态 |

下一个州 x = 0 1 |

展示 输出(Z) |

| 一种 | B C | 1 0 |

B. C |

D E E E. |

1 0 0 1 |

D. E. |

H H. H M. |

0 1 1 0 |

H m |

A. A - |

0 1 1 - |

表:状态表

在这里,由于有七种状态,需要三个D触发器。因此,需要具有4个输入和4个输出的PLA电路。如果考虑了代码转换器的状态分配,则可以写入以下等式的产生从karnaugh导出的产生的输出方程和d触发器输入方程

d1 = q1 + = q2“

d2 = q2 + = q2“

d3 = q3 + = q1 q2 q3 = x“q1 q3”= x q1“q2”

z = x“q3”+ x q3

| x Q1 Q2 Q3 | Z D1 D2 D3 |

- - 0 - - 1 - - - 1 1 1 0 1 - 0 1 0 0 - 0 - - 0 1 - 1 |

0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 1 0 0 0 |

上述方程所对应的PLA表如上表所示。这个表可以用具有4个输入、7个产品项和4个输出的PLA来实现。为初步验证上述设计的运行,假设X=0, Q1Q2Q3=000。这选择表中的行- -0 -和0- - -0,因此Z=0和D1D2D3=100。主时钟边缘后,Q1Q2Q3=100。如果下一个输入是X=1,则选择行- - 0 -和- 1- -,因此Z=0和D1D2D3=110。主时钟边缘后,Q1Q2Q3=110。

可编程逻辑阵列(PLA)

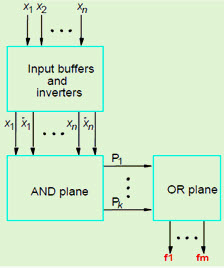

可编程逻辑阵列是一种可编程逻辑设备。它通常用于实现组合逻辑电路。PLA有一套可编程与平面(AND阵列),与一套可编程或平面(OR阵列)相连,然后可临时补充以产生输出。控件中可以合成大量的逻辑函数产品总数(SOP)规范的形式。PLA的简单方框图如下所示。

PLA和PAL(可编程阵列逻辑)的主要区别是,

PLA:两者和飞机和或飞机是可编程的。

PAL:仅和飞机是可编程的,虽然或飞机是固定的。

为了更好地了解PLA,我们在这里考虑以下示例。

让我们尝试实现这些功能F1和F2

将输入x1、x2、x3及其互补信号分别赋给可编程的and平面,得到与平面输出为P1、P2、p3,称为minterms。然后将这些信号发送到可编程OR平面,产生所需的输出函数f1和f2(乘积之和)。下图描述了给定功能的PLA的门级实现。

这一切都是关于使用PLA设计顺序电路。我们认为本文中给出的信息有助于您更好地了解这一概念。此外,关于本文的任何疑问或任何帮助执行电气和电子项目bob体育棋牌bob足球体育app,您可以通过评论下面的评论部分来接近我们。这是一个问题,顺序电路是什么意思?