CMOS晶体管的制造过程

有一个时代,电脑是如此庞大的局部安装它们,容易需要一个房间空间。但今天他们如此发展,我们甚至可以轻松地将它们作为笔记本电脑携带。使这成为可能的创新是集成电路的概念。在集成电路,大量的活跃和被动元素随着他们的互连在一个小硅片上发展,通常是50 × 50密耳的截面。制作此类电路的基本工艺包括外延生长、掩膜杂质扩散、氧化物生长和氧化物蚀刻,使用光刻技术制作图案。

晶片上的组件包括电阻器,晶体管,二极管,电容器等。在IC的最复杂的元素是晶体管。晶体管具有各种类型如CMOS,BJT,FET。我们选择通过IC通过IC实现晶体管技术的类型。在本文中,让我们熟悉概念CMOS制造(或)晶体管的制造为CMOS。

互补金属氧化物半导体工艺

减少功耗要求CMOS技术用于实现晶体管。如果我们需要更快的电路,则晶体管通过IC使用BJT.。制造CMOS晶体管随着IC可以用三种不同的方法进行。

n孔/ p井技术,其中n型扩散在p型衬底或p型扩散上分别通过n型衬底进行。

这双井技术, 在哪里NMOS和PMOS晶体管通过同时在外延生长基础上同时扩散而不是基材来开发晶片上。

在绝缘体过程中的硅,而不是使用硅作为基板的绝缘材料用于提高速度和闩锁易感性。

N井/ P井技术

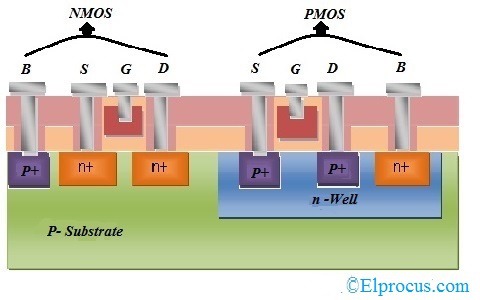

CMOS可以通过集成两者得到NMOS和PMOS晶体管在相同的硅晶片上。在N阱技术中,n型孔在p型衬底上扩散,而在p-well中它是副副本。

CMOS制造步骤

这CMOS制造过程流在使用N-孔/ P井技术制造的同时使用20个基本制造步骤进行。

使用n井制作cmos

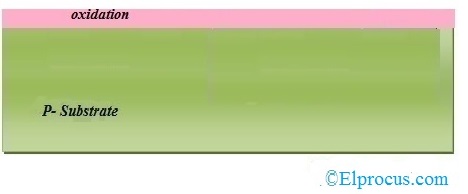

步骤1:首先,我们选择一种衬底作为制造的基础。对于N-阱,选择p型硅衬底。

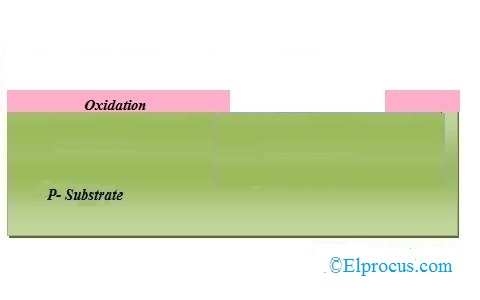

第2步 - 氧化:n型杂质的选择性扩散使用SiO2作为屏障来完成,该屏障保护晶圆片的部分不受衬底的污染。SiO2通过氧化过程布置在约1000的氧化室中将基材暴露于高质量的氧气和氢气中0.C

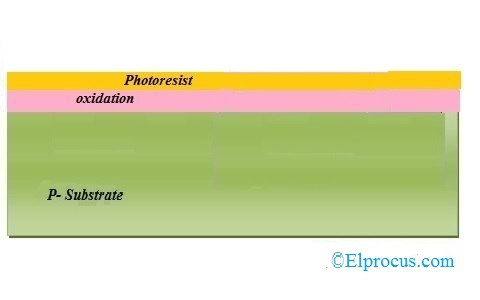

步骤3 - 光致抗蚀剂的生长:在该阶段允许选择性蚀刻,将SiO 2层进行光刻工艺。在该过程中,晶片涂覆有光敏乳液的均匀膜。

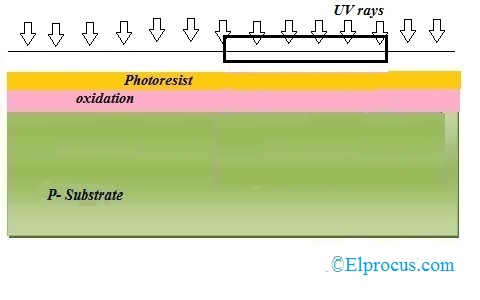

第4步 - 屏蔽:该步骤是光刻过程的延续。在该步骤中,使用模板制造所需的开放模式。该模板用作光致抗蚀剂上的掩模。该基板现在暴露在一起紫外线在掩模的暴露区域下存在的光致抗蚀剂得到聚合。

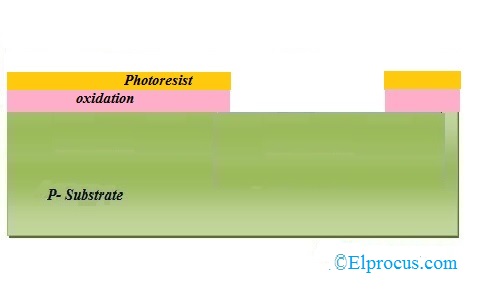

步骤5 - 去除未曝光的光致抗蚀剂:去除掩模,并通过使用诸如三氯乙烯的化学品显影晶片来溶解未曝光的光致抗蚀剂区域。

第6步 - 蚀刻:将晶片浸入氢氟酸的蚀刻溶液中,其从掺杂剂被扩散的区域中除去氧化物。

步骤7 - 去除整个光致抗蚀剂层:在此期间蚀刻过程,由光致抗蚀剂层保护的SiO 2的那些部分不受影响。现在用化学溶剂(热H2SO4)剥离光致抗蚀剂掩模。

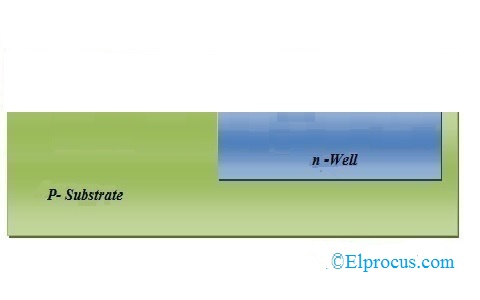

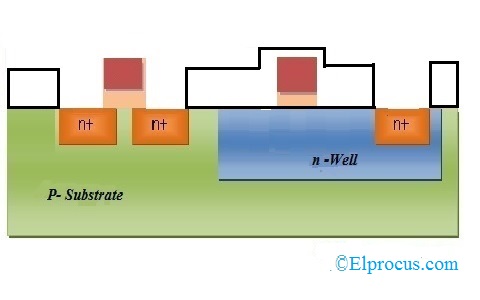

第8步 - 形成n阱:N型杂质通过暴露的区域扩散到p型衬底中,从而形成N-阱。

步骤9 -移除SiO2:现在使用氢氟酸除去SiO 2层。

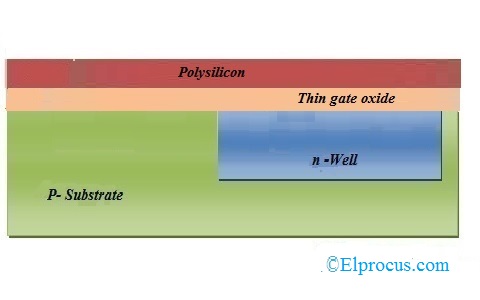

步骤10 - 多晶硅的沉积:a的大门错位CMOS晶体管会导致可能危害电路的不需要的电容。因此,为了防止这种“自对准栅极过程”是优选的,其中使用离子注入在形成源极和漏极之前形成栅极区域。

多晶硅用于形成门,因为它可以承受大于8000的高温0.C当晶片进行退火方法时,用于形成源极和排水管。通过使用沉积多晶硅化学沉积过程在薄层氧化物层上。在多晶硅层下方的该薄栅极氧化物可防止在栅极区域下进一步掺杂。

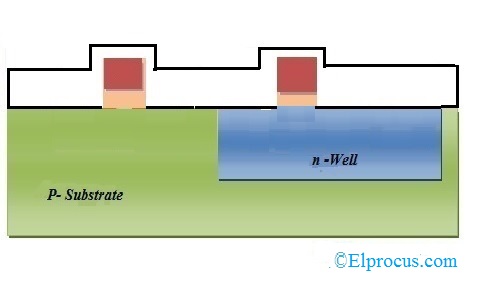

第11步 - 浇口区域的形成:除了形成门所需的两个区域NMOS和PMOS晶体管剥离了多晶硅的剩余部分。

第12步 - 氧化过程:在晶片上沉积氧化层,该晶片可进一步用作屏蔽扩散和金属化过程。

步骤13 - 屏蔽和扩散:为了使N型杂质扩散的区域使用掩蔽工艺进行小间隙。

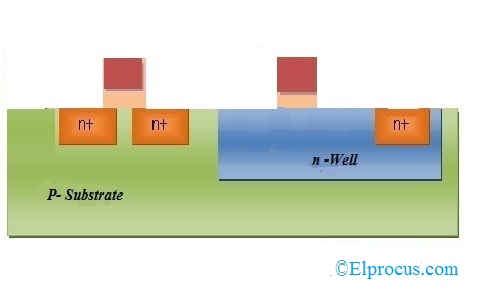

使用扩散过程,开发了三个n +区域,用于形成NMOS末端。

步骤14 -去除氧化物:剥离氧化物层。

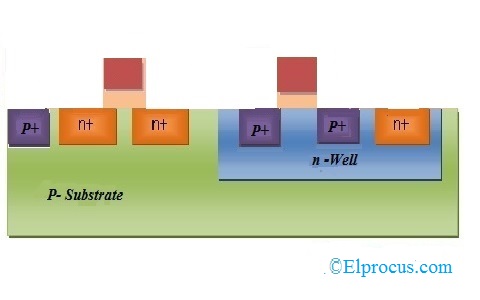

步骤15 - p型扩散:类似于用于形成PMOS p型扩散的端子的n型扩散。

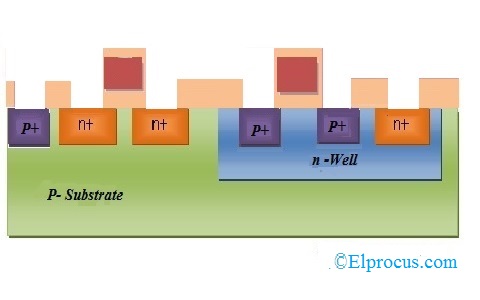

步骤16 - 覆盖厚场氧化物:在形成金属端子之前,布置厚场氧化物以形成晶片的区域的保护层,其中不需要终端。

步骤17 - 金属化:该步骤用于形成可以提供互连的金属终端。铝在整个晶圆上铺展。

步骤18 - 去除多余的金属:从晶片中取出过量的金属。

步骤19 -终端的形成:在移除过量的金属端子以进行互连之后形成的间隙中。

步骤20 - 分配终端名称:名称被分配给终端NMOS和PMOS晶体管。

利用P井技术制作CMOS

除了使用n型衬底之外,P阱过程类似于N阱过程,并进行p型扩散。为简单起见,通常优选N阱过程。

双管制造CMOS

采用双管工艺可以控制P型和n型器件的增益。所涉及的各个步骤互补金属氧化物半导体的制造使用双管方法如下面所述

-

- 拍摄轻微掺杂的N或p型衬底,并使用外延层。外延层保护芯片中的闩锁问题。

-

- 获得了具有实测厚度和精确掺杂浓度的高纯硅层。

-

- 形成P和N阱的管。

-

- 在扩散过程中防止污染的薄氧化物结构。

-

- 使用离子注入方法形成源极和漏极。

-

- 制造用于制造金属触点的部分。

- 用于绘制金属触点的金属化

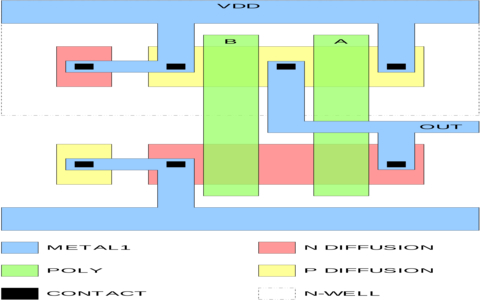

CMOS IC布局

上面的景观一个cmos.制造和布局给出。这里可以清楚地观察各种金属触点和N阱扩散。

因此,这一切都是关于CMOS制造技术。让我们考虑一个1范围的晶片分为50密耳的400个表面积50密耳芯片。它需要一个50 mil2的面积,以制造晶体管。因此,每个IC包含2个晶体管,因此存在2×400 = 800个构建在每个晶片上的晶体管。如果处理了10个晶片,则每个批次然后可以同时制造8000个晶体管。您在IC上观察到了各种组件是什么?