什么是PAL和PLA,设计和差异?

早些时候,设计的设计逻辑电路可以用小规模集成逻辑门等组件,多路复用器、解复用器、FFs等。但是,现在一个可编程逻辑器件可以取代所有这些SSI元件。这就是SSI行业相对于可编程逻辑器件(PLD)减少的原因,而SSI在许多应用中都得到了应用。的可编程逻辑设备或PLD是一种用于实现逻辑电路的一种芯片。它包括一组可以以多种方式修改的一组逻辑电路元件。PLD看起来像一个黑匣子,由可编程交换机和逻辑门组成。交换机的主要功能是让PLD内的逻辑门相互关联以执行逻辑电路。PLD分为不同类型,如SPLD-Simple PLD(中国人民解放军&朋友),CPLD-复杂的PLD,fpga。现场可编程门阵列.这篇文章讨论了什么是PAL和PLA,设计和他们的区别。

什么是PAL和PLA?

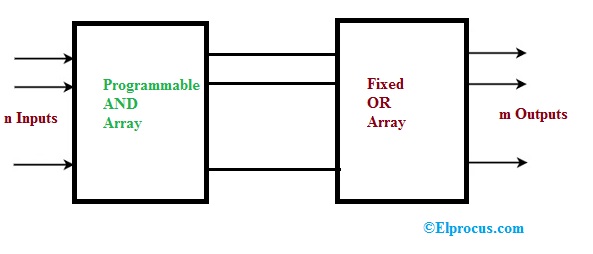

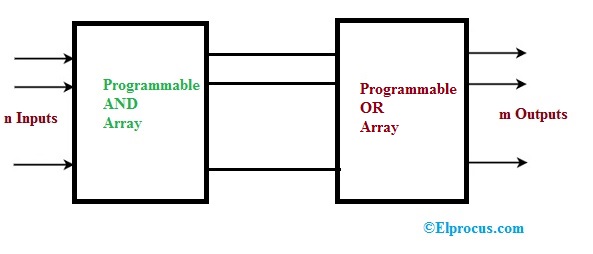

两个都可编程序逻辑阵列和可编程序逻辑阵列是PLD的类型(可编程逻辑设备),这些主要用于通过顺序逻辑相互设计组合逻辑。这两个主要区别在于,PAL可以设计有一系列和闸门和固定的或门的固定集合,而PLA可以设计有一个可编程阵列的和虽然固定的或门。可编程逻辑设备提供简单的逻辑电路设计。

以前可编程逻辑设备,组合逻辑电路可以使用多路复用器设计,这些电路刚刚以及化合物,然后开发PLD。初始可编程逻辑设备是ROM,但由于硬件浪费问题以及每个硬件应用程序中的指数增长增强,它并不成功。克服这个问题,使用PAL和PLA。这两个是可编程的,有效地使用硬件。

可编程阵列逻辑(PAL)的设计

的术语PAR或可编程数组逻辑的定义是一种称为可编程逻辑器件电路的PLD,并且该PAL的工作与PLA相同。可编程阵列逻辑的设计可以用固定或栅极以及可编程和栅极来完成。通过使用这一点,我们可以在任何与每个或门的关联和栅极都表示两个可以以何种形式生产的产品条件数量SOP(产品总和)确切的功能。

因为像AND这样的逻辑门是连续地连接到OR门的,这表明产生的乘积项不是与输出函数一起分布的。PLD开发背后的主要概念是通过去除有缺陷的布线,避免逻辑设计,并降低功耗,在单个芯片上制造一个复合布尔逻辑。

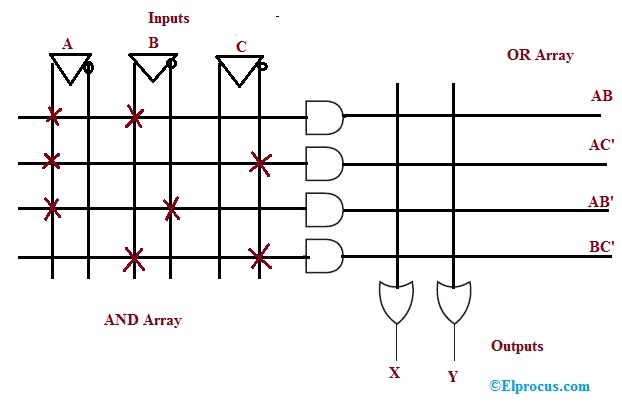

朋友的例子

实施以下内容布尔表达式借助于可编程阵列逻辑

X = ab + ac '

Y= ab ' + bc '

上面给了两个布尔函数是一种形式SOP(产品总和).布尔表达式中的乘积项是X和Y,在每个方程中有一个乘积项是AC '。因此,生成上述两个方程所需的逻辑门是AND门-4或可编程门-2。对应的PAL逻辑图如下图所示。

可编程的和门具有正常和补充可变输入的入口权。在上面的逻辑图中,每个和门的可用输入是A, A ', B, B ', C, C '。因此,为了用每个AND门生成一个单独的产品术语,需要这个程序。

所有产品术语都可以在每个或门的输入处获得。在这里,逻辑门上的可编程连接可以用符号“X”表示。

这里,OR门输入是固定的。因此,所需的产品术语与每个OR门输入相关联。因此,这些门将生成特定的布尔方程。的'。'符号表示永久连接。

设计可编程逻辑阵列(PLA)

术语PLA的定义以乘积和(SOP)的形式表示布尔函数。该可编程逻辑阵列的设计可以通过与、或、非等逻辑门在芯片上制造来实现,使每一个输入及其辅助都可以通向每一个与门。

每个和门的输出都连接到每个或门。最后,OR门的输出产生芯片的输出。因此,这就是如何完成适当的关联以使用产品总和的表达式。在可编程逻辑阵列中,逻辑门的连接如和或或是可编程的。PLA昂贵且难以与PAL比较。PAL使用两种不同的开发方法可用于可编程逻辑阵列,用于增强编程的不断努力。在这种方法中,可以在每个交叉点上使用熔断器进行每个连接,无需熔丝吹送不必要的连接。最终技术接合连接的同时使用用于精确互连模型的合适盖的制造过程。

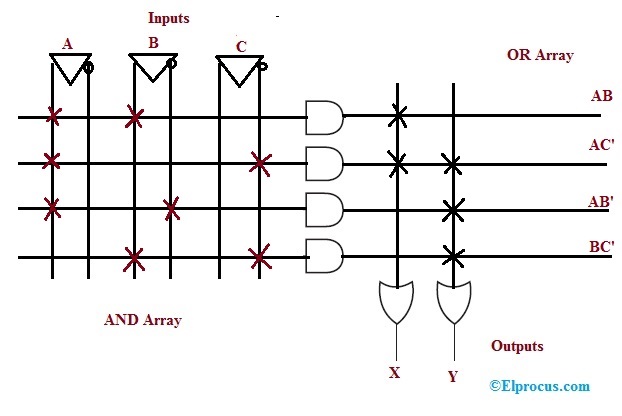

解放军的例子

使用可编程逻辑阵列(PLA)实现以下布尔表达式

X = ab + ac '

Y = ab ' + bc ' + ac '

上面给出的两个布尔函数以SOP(产品之和)的形式表示。布尔表达式中的乘积项是X和Y,在每个方程中有一个乘积项是AC '。因此,生成上述两个方程所需的逻辑门是和门-4,或可编程或门-2。等效的PLA逻辑图如下所示。

可编程的和门具有正常和补充可变输入的入口权。在上面的逻辑图中,每个和门的可用输入是A, A ', B, B ', C, C '。因此,为了用每个AND门生成一个单独的产品术语,需要这个程序。

所有的产品条款可在每个或门的输入。在这里,逻辑门上的可编程连接可以用符号“X”表示。

PAL和PLA的区别

的PAL和PLA在表格中的区别主要包括PAL和PLA的完整形式、构造、可用性、灵活性、成本、功能数量和速度,这些将在下面讨论。

| 可编程阵列逻辑 | 可编程逻辑阵列(PLA) |

| 全文的PAL是可编程数组逻辑 | PLA的完整形式是一个可编程逻辑阵列 |

| 利用可编程的与与或门的集合可以实现PAL的构造 | 可以使用可编程收集和固定收集或门的可编程集合来完成PLA的构造。 |

| PAL的可用性较不平衡 | PLA的可用性更多 |

| PAL编程的灵活性更大 | PLA的灵活性较少 |

| PAL的成本很昂贵 | PLA的成本是中间范围 |

| PAL中实施的职能数量很大 | PLA中实现的功能的数量是有限的 |

| PAL的速度很慢 | 解放军的速度很高 |

因此,这都是关于PAL和PLA的。从上面的信息,最后,我们可以得出结论,这些是可编程逻辑器件(pld)可编程序逻辑阵列比可编程阵列逻辑更灵活。但是,可编程阵列逻辑可以毫不费力地生成一个组合逻辑电路。这里有个问题要问你,它的作用是什么数字电子学中的PAL和PLAbob足球体育app?