什么是控制单元:元件及其设计

控制单元是计算机中中央处理单元(CPU)的主要组成部分,在程序执行过程中,它通过控制来指导操作处理器/电脑。控制单元的主要功能是从计算机的存储器中取出并执行指令。它接收用户输入的指令/信息,并将其转换成控制信号,然后交给CPU进行进一步的执行。它是由John Neumann开发的Von Neumann架构的一部分。它负责提供定时信号和控制信号,并指导CPU程序的执行。在现代计算机中,它是作为中央处理器的内部部件。本文描述了控制单元的完整信息。

什么是控制单元?

接收来自用户的输入信号/信息/指令,并将其转换成控制信号以便在CPU中执行的部件。它控制和指导主存储器、算术逻辑单元(ALU)、输入和输出设备,并负责发送到计算机中央处理器的指令。它从主内存表示处理器并发送给处理器的指令寄存器,其中包含寄存器的内容。

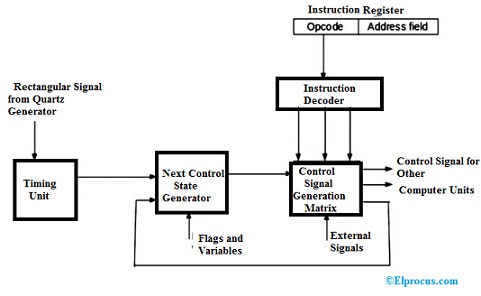

控制单元将输入转换成控制信号,然后发送到处理器并指导程序的执行。必须执行的操作是由计算机上的处理器指导的。主要有中央处理器(CPU)和图形处理单元(GPU)需要一个控制单元作为内部部件。控制单元框图如图所示。

控制单元的组成

本单元的组成部分是教学寄存器、CPU内部的控制信号、总线进出的控制信号、控制总线、输入标志和时钟信号。

硬件控制单元由指令寄存器(包含操作码和地址字段)、时序单元、控制状态组成发电机、控制信号生成矩阵、指令解码器。

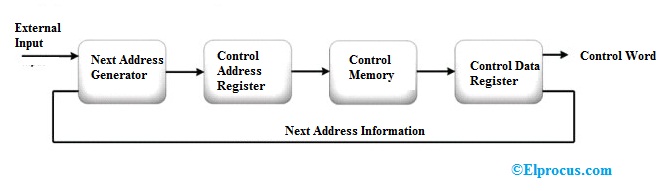

微程序控制单元的组成部分是下一个地址发生器,一个控制地址寄存器,控制存储器和控制数据寄存器。

功能

的控制单元的功能包括以下。

- 它指导处理器和其他设备之间的数据序列流动。

- 它可以解释指令并控制处理器中的数据流。

- 它从从指令寄存器接收到的指令或命令中生成控制信号序列。

- 它负责控制计算机CPU中的执行单元,如ALU、数据缓冲区和寄存器。

- 它具有获取、解码、处理执行和存储结果的能力。

- 它不能处理和存储数据

- 为了传输数据,它与输入输出设备进行通信,并控制计算机的所有单元。

控制单元设计

这个设计可以用两个来完成控制单元的类型其中包括以下内容。

- 硬线的基础

- 基于微程序的(单级和两级)

电路的控制单元

硬连线控制单元的基本设计如上所示。这种类型的控制信号是由一个特殊的硬件产生的逻辑电路电路结构没有任何变化。在这种情况下,生成的信号不能被修改以便在处理器中执行。

一个操作码(指令的操作码)的基本数据被送到指令解码器进行解码。指令译码器用于解码操作码中不同类型的数据的解码器集合。这导致输出信号包含主动信号的值,这些主动信号作为矩阵发生器的输入来产生控制信号,以便由计算机的处理器执行程序。

矩阵发生器提供控制单元的状态和处理器输出的信号(中断信号)。矩阵是作为可编程序逻辑阵列.由矩阵发生器产生的控制信号作为下一个发生器矩阵的输入,并与包含矩形图案的定时单元的定时信号相结合。

为了获取新指令,控制单元成为执行新指令的初始阶段。只要计算机的定时信号、输入信号和指令状态不变,控制单元就保持在初始阶段或第一阶段。如果所生成的任何信号有任何变化,就可以引发控制单元状态的变化。

当外部信号或中断发生时,控制单元进入下一个状态并对中断信号进行处理。标志和状态用于选择执行指令执行周期所需的状态。

在最后一种状态下,控制单元获取下一条指令并将其输出送到程序计数器,然后送到内存地址寄存器,再送到缓冲区寄存器,最后送到指令寄存器读取指令。最后,如果最后一条指令(由控制单元获取)是结束指令,那么它将进入处理器的操作状态,直到用户指示下一个程序为止。

微程序控制单元

在这种类型中,控制存储器用于存储在程序执行期间编码的控制信号。由于微程序将地址域存储在控制存储器中,因此控制信号不会立即生成并被解码。整个过程是一个单一的层次。

微操作是为了执行程序中的微指令而进行的。微程序控制单元的框图如图所示。从图中,微指令的地址是由控制存储器地址寄存器获得的。控制单元的所有信息都永久地存储在称为ROM的控制存储器中。

控制存储器中的微指令由控制寄存器保存。由于微指令以控制字(包含二进制控制值)的形式存在,需要执行1个或多个微操作来进行数据处理。

在微指令执行过程中,下一个地址生成器计算微指令的下一个地址,然后发送到控制地址寄存器读取下一个微指令。

微程序的微操作序列由下一个地址发生器执行,并作为微程序序器来获取序列地址,即从控制存储器中读取。

Verilog控制单元代码

控制单元的Verilog代码如下所示。

包括“prj_definition.v”

模块控制单元(MEM_DATA, RF_DATA_W, RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2, RF_READ, RF_WRITE, ALU_OP1, ALU_OP2, ALU_OPRN, MEM_ADDR, MEM_READ, MEM_WRITE, RF_DATA_R1, RF_DATA_R2, ALU_RESULT, 0, CLK, RST)

/ /输出信号

//寄存器文件的输出

输出[' DATA_INDEX_LIMIT: 0] RF_DATA_W;

output [' ADDRESS_INDEX_LIMIT:0] RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2;

输出RF_READ RF_WRITE;

//输出ALU

输出[' DATA_INDEX_LIMIT:0] ALU_OP1, ALU_OP2;

输出[' ALU_OPRN_INDEX_LIMIT: 0] ALU_OPRN;

//输出内存

输出[' ADDRESS_INDEX_LIMIT: 0] MEM_ADDR;

输出MEM_READ MEM_WRITE;

/ /输入信号

input [' DATA_INDEX_LIMIT:0] RF_DATA_R1, RF_DATA_R2, ALU_RESULT;

输入0,CLK, RST;

/ / Inout信号

inout [' DATA_INDEX_LIMIT: 0] MEM_DATA;

/ /状态网

线[2:0]proc_state;

//保存程序计数器值,存储当前指令,堆栈指针寄存器

reg MEM_READ MEM_WRITE;

reg MEM_ADDR;

reg ALU_OP1 ALU_OP2;

reg ALU_OPRN;

reg RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2;

reg RF_DATA_W;

Reg [1:0] state, next_state;

PROC_SM state_machine (.STATE (proc_state) .CLK(时钟),首要(RST));

always @ (posedge CLK)

开始

如果(RST)

国家< = RST;

其他的

国家< = next_state;

结束

总是@(状态)

开始

MEM_READ = 1 'b0;MEM_WRITE = 1 'b0;MEM_ADDR = 1 'b0;

ALU_OP1 = 1 'b0;ALU_OP2 = 1 'b0;ALU_OPRN = 1 'b0;

RF_ADDR_R1 = 1 'b0;RF_ADDR_R2 = 1 'b0;RF_ADDR_W = 1 'b0;RF_DATA_W = 1 'b0;

例(状态)

“PROC_FETCH:开始

next_state = ' PROC_DECODE;

MEM_READ = 1 'b1;

RF_ADDR_R1 = 1 'b0;RF_ADDR_R2 = 1 'b0;

RF_ADDR_W = 1 'b1;

结束

“PROC_DECODE:开始

next_state = ' PROC_EXE;

MEM_ADDR = 1 'b1;

ALU_OP1 = 1 'b1;ALU_OP2 = 1 'b1;ALU_OPRN = 1 'b1;

MEM_WRITE = 1 'b1;

RF_ADDR_R1 = 1 'b1;RF_ADDR_R2 = 1 'b1;

结束

“PROC_EXE:开始

next_state = ' PROC_MEM;

ALU_OP1 = 1 'b1;ALU_OP2 = 1 'b1;ALU_OPRN = 1 'b1;

RF_ADDR_R1 = 1 'b0;

结束

“PROC_MEM:开始

next_state = ' PROC_WB;

MEM_READ = 1 'b1;MEM_WRITE = 1 'b0;

结束

“PROC_WB:开始

next_state = ' PROC_FETCH;

MEM_READ = 1 'b1;MEM_WRITE = 1 'b0;

结束

endcase

结束

endmodule;

模块PROC_SM(状态、CLK RST);

//输入列表

输入时钟,RST;

//输出列表

输出(2:0)状态;

/ /输入列表

输入时钟,RST;

/ /输出列表

输出状态;

注册(2:0)状态;

注册(1:0)状态;

reg 1:0 [] next_state;

reg PC_REG, INST_REG, SP_REF;

“定义PROC_FETCH 3 'h0

“定义PROC_DECODE 3 'h1

“定义PROC_EXE 3 'h2

“定义PROC_MEM 3 'h3

“定义PROC_WB 3 'h4

//状态初始化

最初的

开始

国家= 2 'bxx;

next_state = ' PROC_FETCH;

结束

//复位信号处理

always @ (posedge RST)

开始

状态= ' PROC_FETCH;

next_state = ' PROC_FETCH;

结束

always @ (posedge CLK)

开始

状态= next_state;

结束

总是@(状态)

开始

if (state === ' PROC_FETCH ')

开始

next_state = ' PROC_DECODE;

print_instruction (INST_REG);

结束

if (state === ' PROC_DECODE ')

开始

next_state = ' PROC_EXE;

结束

if (state === ' PROC_EXE ')

开始

next_state = ' PROC_MEM;

print_instruction (SP_REF);

结束

if (state === ' PROC_MEM ')

开始

next_state = ' PROC_WB;

结束

if (state === ' PROC_WB ')

开始

next_state = ' PROC_FETCH;

print_instruction (PC_REG);

结束

结束

任务print_instruction;

输入[' DATA_INDEX_LIMIT: 0]本月;

reg[5:0]操作码;

reg 4:0 [] rs;

reg 4:0 [] rt;

reg 4:0 [] rd;

reg 4:0 [] shamt;注册(5:0)功能;reg[15:0]立即;注册(25:0)地址;

开始

//解析指令

/ /异形战机

{opcode, rs, rt, rd, shamt, function} = inst;

/ / i类型

{opcode, rs, rt, immediate} = inst;

/ / j

{opcode, address} = inst;

$write(" @ %6dns -> [0X%08h] ", $time, inst);

(操作码)/ /异形战机

6 'h00:开始

用例(功能)

6 'h20: $写(“添加[% 2 d], r (% 2 d), r (% 2 d);“,rs, rt, rd);

6 'h22: $写(“子(% 2 d), r (% 2 d), r (% 2 d);“,rs, rt, rd);

6 'h2c: $写(“mul (% 2 d), r (% 2 d), r (% 2 d);“,rs, rt, rd);

6 'h24: $写(“和[% 2 d], r (% 2 d), r (% 2 d);“,rs, rt, rd);

6 'h25:写美元(或r [% 2 d], [% 2 d], r (% 2 d);“,rs, rt, rd);

6 'h27: $写(“和[% 2 d], r (% 2 d), r (% 2 d);“,rs, rt, rd);

6 'h2a: $写(“slt r [% 2 d], [% 2 d], r (% 2 d);“,rs, rt, rd);

6 'h00: $写(“sll r (% 2 d), % 2 d r (% 2 d);“,rs, shamt, rd);

6 'h02: $写(“srl r (% 2 d), 0 x % 2 h, r (% 2 d);“,rs, shamt, rd);

6'h08: $write(" jr r[%02d]; ", rs);

默认值:$写(" ");

endcase

结束

/ / i类型

6 'h08: $写(“另外r [% 2 d], [% 2 d], 0 x % 04 h;”,rs, rt,立即);

6 'h1d: $写(“慕蠡r [% 2 d], [% 2 d], 0 x % 04 h;”,rs, rt,立即);

6 'h0c: $写(“我[% 2 d], r (% 2 d), 0 x % 04 h;”,rs, rt,立即);

6 'h0d: $写(“ori r [% 2 d], [% 2 d], 0 x % 04 h;”,rs, rt,立即);

6'h0f: $write(" lui r[%02d], 0X%04h; ", rt,立即);

6 'h0a: $写(“slti r [% 2 d], [% 2 d], 0 x % 04 h;”,rs, rt,立即);

6 'h04: $写(“说真的[% 2 d], r (% 2 d), 0 x % 04 h;”,rs, rt,立即);

6 'h05: $写(“bne r [% 2 d], [% 2 d], 0 x % 04 h;”,rs, rt,立即);

6 'h23: $写(“lw r [% 2 d], [% 2 d], 0 x % 04 h;”,rs, rt,立即);

6 'h2b: $写(“sw r [% 2 d], [% 2 d], 0 x % 04 h;”,rs, rt,立即);

/ / j

6'h02: $write(" jmp 0X%07h; ",地址);

6'h03: $write(" jal 0X%07h; ",地址);

6 'h1b: $写(“推动;”);

6 'h1c: $写(“流行;”);

默认值:$写(" ");

endcase

写美元(“\ n”);

结束

endtask

端模块;

常见问题

1).控制单元的工作是什么?

控制单元的工作是指挥数据流或指令由计算机的处理器执行。它控制、管理和协调主存储器、ALU、寄存器、输入和输出单元。它获取指令并为执行生成控制信号。

2).控制内存是什么?

控制存储器通常是RAM或ROM,用来存储控制寄存器的地址和数据。

威尔克斯控制单元是什么?

顺序和组合电路由威尔克斯控制单元取代了硬接线控制单元。它使用一个存储单元来存储微程序的指令序列。

4).什么是硬连线控制单元?

该硬连线控制单元在电路中不发生任何物理变化的情况下,通过在每个时钟脉冲中从一种状态切换到另一种状态来产生控制信号。控制信号的生成依赖于指令寄存器、解码器和中断信号。

5).控制内存是什么?

控制单元的信息或数据被暂时或永久地存储在控制存储器中。

控制内存有两种类型。它们是随机存取存储器(RAM)和只读存储器(ROM)。

因此,这一切都是关于定义、组件、设计、图表、函数和控制单元的类型.这里有一个问题,“控制地址寄存器的目的是什么?”